# Circuits and Techniques for All-Digital Frequency Synthesizers and Design Automation

by

Kyumin Kwon

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical and Computer Engineering) in the University of Michigan 2023

#### **Doctoral Committee:**

Professor David Wentzloff, Chair Professor Michael Flynn Associate Professor Ronald Dreslinski Associate Professor Hun-Seok Kim

## Kyumin Kwon

kmkwon@umich.edu

ORCID iD: 0000-0001-9880-0775

© Kyumin Kwon 2023

# **Table of Contents**

| List of Figures                                                            | iv         |

|----------------------------------------------------------------------------|------------|

| List of Tables                                                             | ix         |

| Abstract                                                                   | X          |

| Chapter 1 Introduction                                                     | 1          |

| 1.1 Increasing Demand for Analog Design Automation in sub-20nm Technology  | 1          |

| 1.2 Next Step for Synthesizable Phase Locked Loops                         | 3          |

| 1.3 Need for Low-Jitter Frequency Synthesizers                             | 5          |

| 1.4 Thesis Contributions                                                   | 6          |

| Chapter 2 Design Automation of Synthesizable PLL and a Calibration-free F  | eedforward |

| Technique                                                                  | 7          |

| 2.1 Introduction                                                           | 7          |

| 2.2 Cell-based Architecture                                                | 7          |

| 2.3 Overall Design Automation Flow                                         | 9          |

| 2.3.1 Modeling DCO and PLL                                                 | 10         |

| 2.3.2 Design Solution Searcher                                             | 13         |

| 2.3.3 Back-End Flow                                                        | 14         |

| 2.4 Design Examples and Measurement Results                                | 15         |

| 2.5 Calibration-free Feedforward Technique                                 | 17         |

| 2.5.1 Edge Selecting Feedforward Scheme                                    | 18         |

| 2.5.2 Linearized Noise Analysis                                            | 19         |

| 2.6 Synthesizable Feedforward PLL Measurement Results                      | 27         |

| 2.7 Conclusion                                                             | 28         |

| Chapter 3 PLL Fractional Spur's Impact on FSK Spectrum and a Synthesizable | ADPLL for  |

| a Bluetooth Transmitter                                                    | 30         |

| 3.1 Introduction                                                                                                                                                                                                | 30                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 3.2 Prediction of BLE-TX Spurious Tones from PLL Fractional Spu                                                                                                                                                 | ars 33                                                                                                                    |

| 3.2.1 Fractional Spur Positions                                                                                                                                                                                 | 33                                                                                                                        |

| 3.2.2 Semi-analytical Model of BLE Fractional Spurs                                                                                                                                                             | 36                                                                                                                        |

| 3.2.3 Experimental Results                                                                                                                                                                                      | 41                                                                                                                        |

| 3.3 Proposed All Digital BLE Transmitter                                                                                                                                                                        | 43                                                                                                                        |

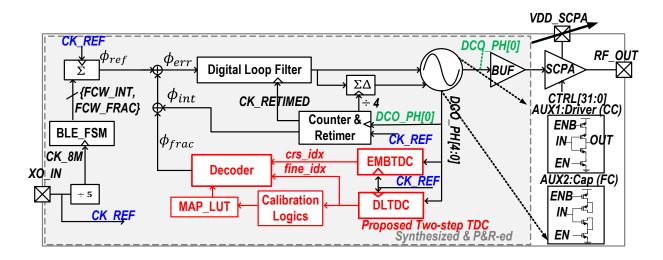

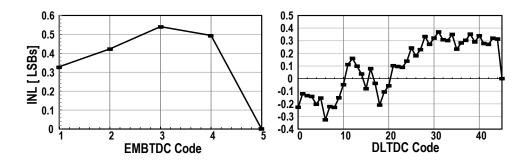

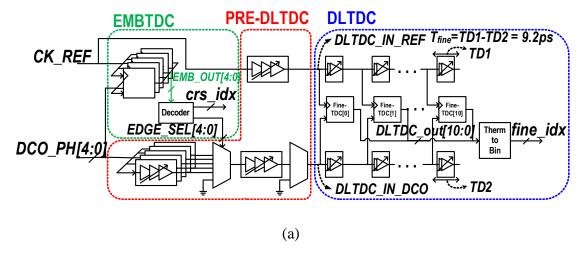

| 3.3.1 Proposed Two-step TDC                                                                                                                                                                                     | 46                                                                                                                        |

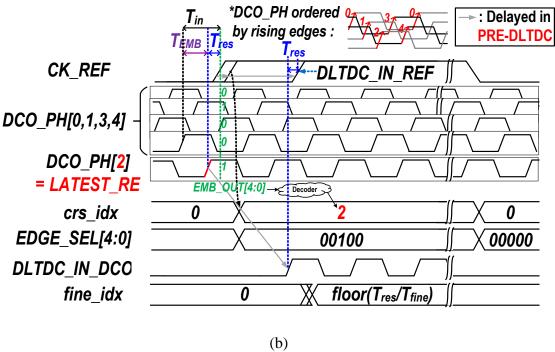

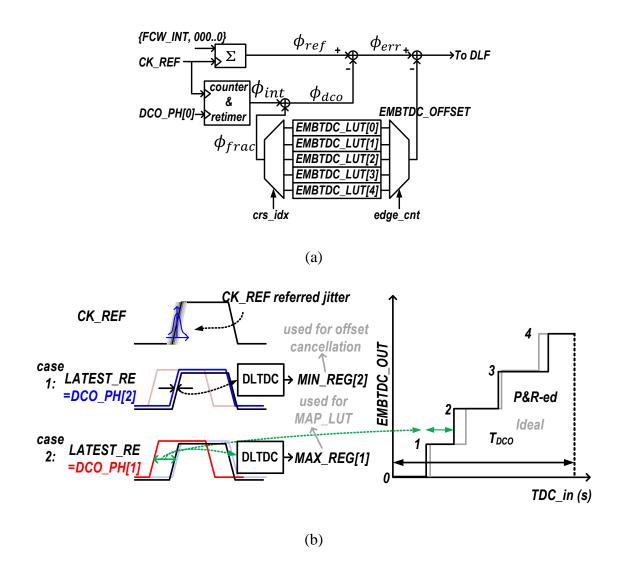

| 3.3.2 Proposed Calibration Scheme                                                                                                                                                                               | 48                                                                                                                        |

| 3.3.3 Circuit Implementation                                                                                                                                                                                    | 52                                                                                                                        |

| 3.3.4 Switched Capacitor Power Amplifier                                                                                                                                                                        | 54                                                                                                                        |

| 3.3.5 Design Automation and Open Source                                                                                                                                                                         | 55                                                                                                                        |

| 3.4 Measurement Results                                                                                                                                                                                         | 56                                                                                                                        |

| 3.5 Conclusion                                                                                                                                                                                                  | 64                                                                                                                        |

|                                                                                                                                                                                                                 |                                                                                                                           |

| Chapter 4 Sub-400fs Low-Jitter Ring Oscillator based Fract                                                                                                                                                      | ional-N MDLL with Reference                                                                                               |

| Chapter 4 Sub-400fs Low-Jitter Ring Oscillator based Fract Triggered Ring Oscillator                                                                                                                            | ional-N MDLL with Reference  66                                                                                           |

| •                                                                                                                                                                                                               |                                                                                                                           |

| Triggered Ring Oscillator                                                                                                                                                                                       | 66                                                                                                                        |

| Triggered Ring Oscillator  4.1 Introduction                                                                                                                                                                     | <b>66</b> 66                                                                                                              |

| Triggered Ring Oscillator  4.1 Introduction 4.2 Proposed Fractional-N MDLL                                                                                                                                      | 66 66 Error! Bookmark not defined.                                                                                        |

| Triggered Ring Oscillator  4.1 Introduction 4.2 Proposed Fractional-N MDLL 4.3 Circuit Implementation                                                                                                           | 66 Error! Bookmark not defined. Error! Bookmark not defined.                                                              |

| Triggered Ring Oscillator  4.1 Introduction 4.2 Proposed Fractional-N MDLL 4.3 Circuit Implementation 4.4 Measurement and Simulation Results                                                                    | 66 Error! Bookmark not defined. Error! Bookmark not defined. Error! Bookmark not defined.                                 |

| Triggered Ring Oscillator  4.1 Introduction 4.2 Proposed Fractional-N MDLL 4.3 Circuit Implementation 4.4 Measurement and Simulation Results 4.5 Conclusion  Chapter 5 Conclusion                               | 66 Error! Bookmark not defined. Error! Bookmark not defined. Error! Bookmark not defined. Error! Bookmark not defined.    |

| Triggered Ring Oscillator  4.1 Introduction 4.2 Proposed Fractional-N MDLL 4.3 Circuit Implementation 4.4 Measurement and Simulation Results 4.5 Conclusion                                                     | 66 Error! Bookmark not defined. Error! Bookmark not defined. Error! Bookmark not defined. Error! Bookmark not defined. 79 |

| Triggered Ring Oscillator  4.1 Introduction 4.2 Proposed Fractional-N MDLL 4.3 Circuit Implementation 4.4 Measurement and Simulation Results 4.5 Conclusion  Chapter 5 Conclusion  5.1 Summary of Contributions | 66 Error! Bookmark not defined. Error! Bookmark not defined. Error! Bookmark not defined. Error! Bookmark not defined. 79 |

# **List of Figures**

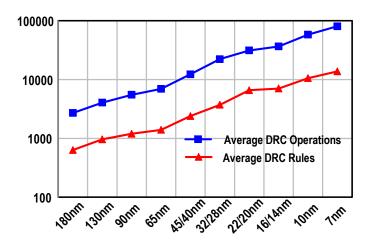

| Figure 1.1 Trend of DRC rules and operations [1]                                     |

|--------------------------------------------------------------------------------------|

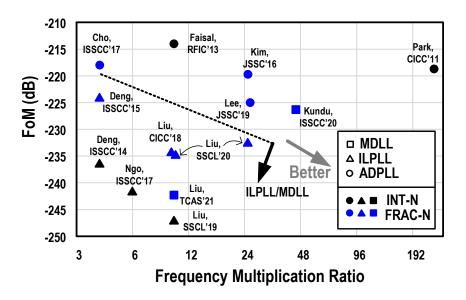

| Figure 1.2 FoM and frequency multiplication ratio of published synthesizable PLLs. 4 |

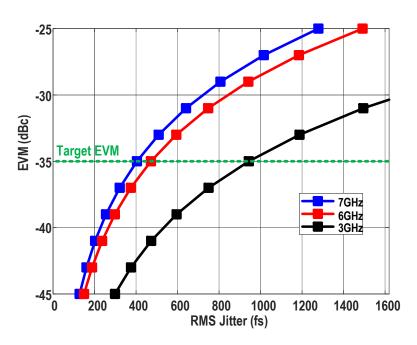

| Figure 1.3 Jitter vs EVM plot for 5G communication system in FR1 band (<7GHz) 5      |

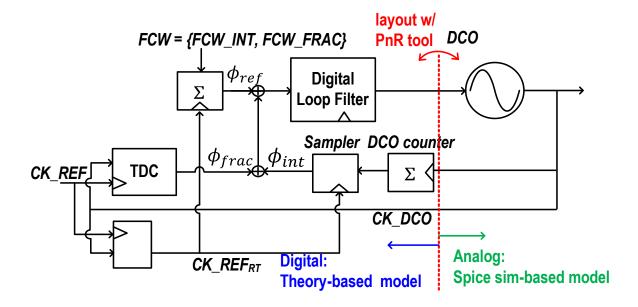

| Figure 2.1 Fully-synthesizable ADPLL architecture and the modeling approach for      |

| Digital and Analog portion.                                                          |

| Figure 2.2 Cell-based DCO architecture with its design variables and the 2 auxiliary |

| cells9                                                                               |

| Figure 2.3 Overall automation flow                                                   |

| Figure 2.4 Design solution searching process with different modeling method for DCO- |

| level and PLL-level. NTF1, 2, 3 are noise transfer functions from each noise source  |

| to the phase of the output clock. Q-noise indicates quantization noise               |

| Figure 2.5 Example layouts of PLLs in GF 12nm (left) and TSMC 65nm (right) 15        |

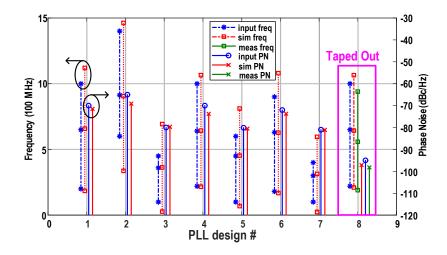

| Figure 2.6 Performance comparison of 8 Generated PLL designs for different input     |

| specifications                                                                       |

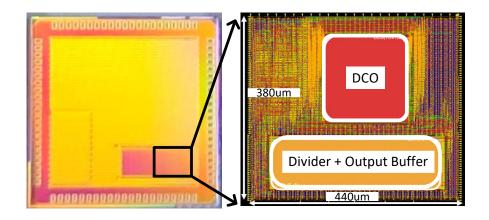

| Figure 2.7 Die photo of the fabricated PLL as part of SoC in TSMC 65nm               |

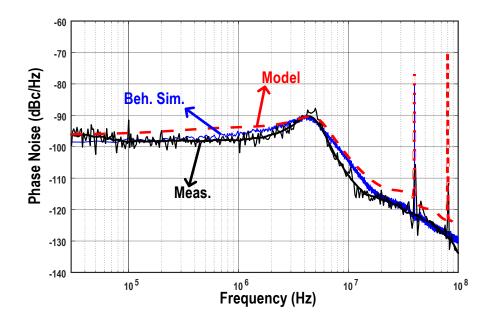

| Figure 2.8 Phase noise comparison between measurement, model and simulation results  |

| at 840MHz                                                                            |

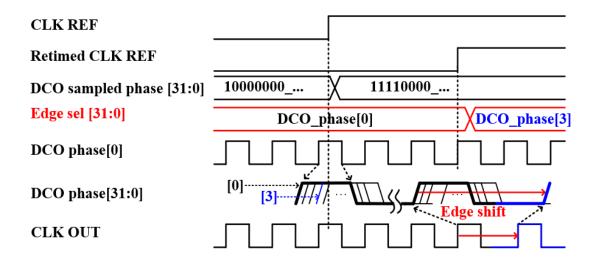

| Figure 2.11 Timing diagram of the edge selection process                             |

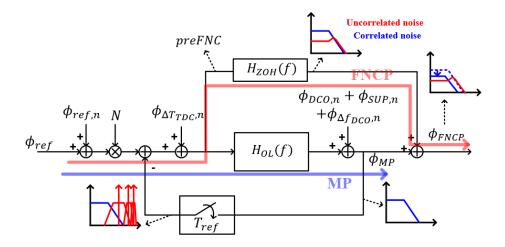

| Figure 2.12 Linearized phase domain model for the proposed PLL                       |

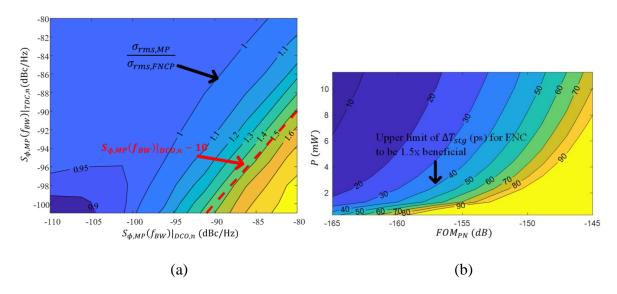

| Figure 2.13 Performance comparison of MP and FNCP in two different environments.     |

| PN plots when (a) DCO noise dominates, (b) TDC noise dominates. Time domain          |

| simulation plot when (c) DCO noise dominates, (d) TDC noise dominates 26             |

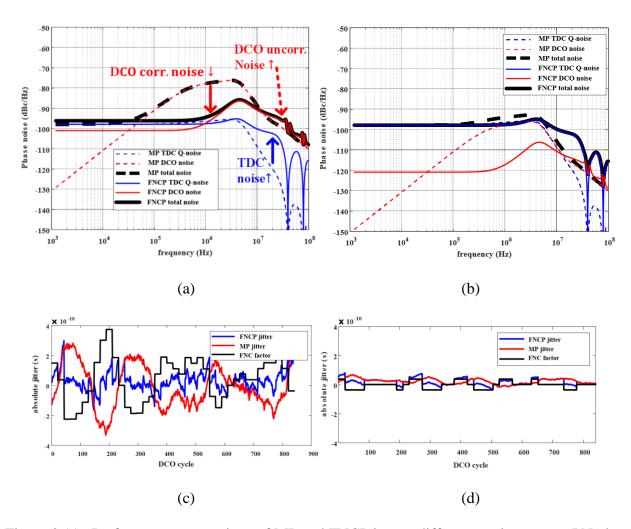

| Figure 2.14 Contour plots of (a) jitter improvement by FNC with MP in-band PN level                            |

|----------------------------------------------------------------------------------------------------------------|

| due to DCO on x-axis and TDC on y-axis, (b) required maximum delay per DCO                                     |

| stage for FNC to be 1.5x beneficial                                                                            |

| Figure 2.15 Measured phase noise (meas.) in comparison with the analytical model                               |

| (model) when (a) DCO noise dominates and (b) TDC noise dominates                                               |

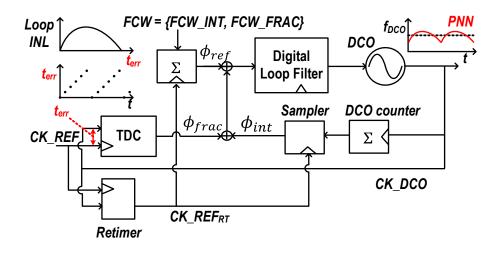

| Figure 3.1 Phase Domain ADPLL block diagram with loop INL with respect to <i>terr</i> 34                       |

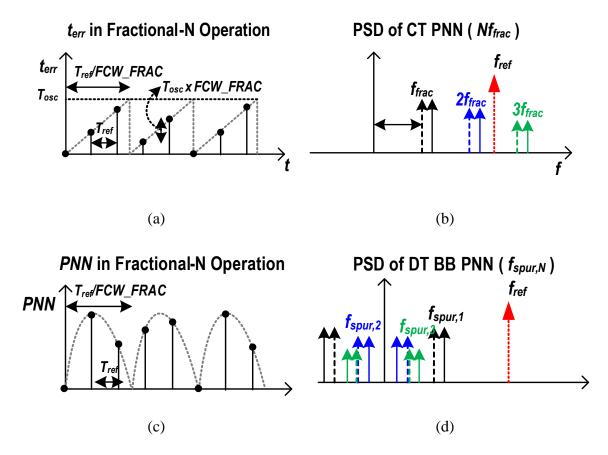

| Figure 3.2 Conceptual illustration of (a) $t_{err}[N_{ref}]$ , (b) PSD of CT PNN, (c) time domain              |

| of DT PNN, (d) PSD of DT baseband PNN                                                                          |

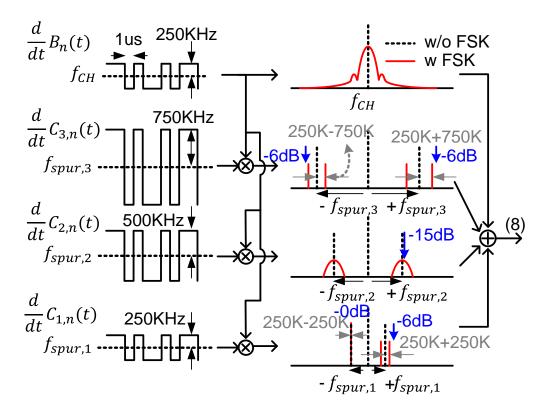

| Figure 3.3 Conceptual illustration of the impact of modulation on fractional spurs of                          |

| equation (8)                                                                                                   |

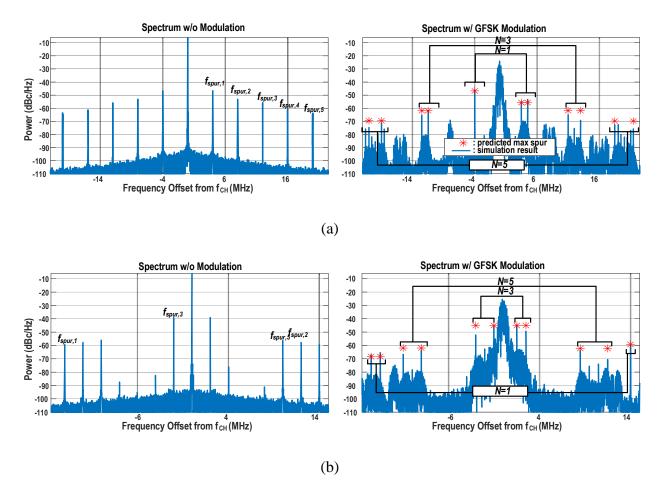

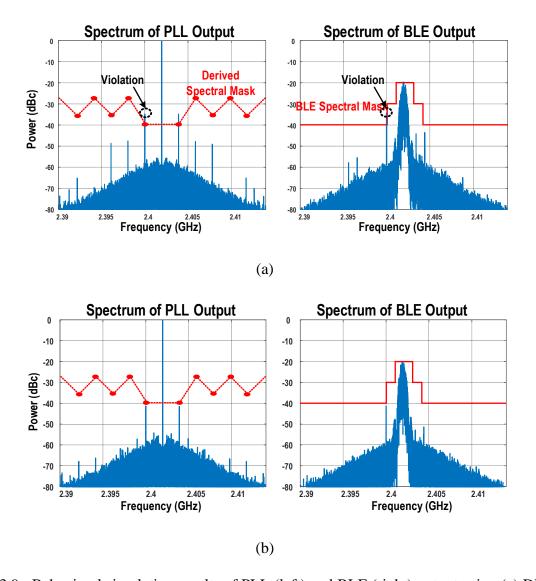

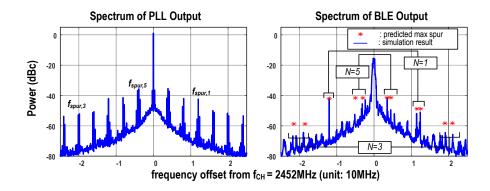

| Figure 3.4 Simulated PLL and BLE spectrum and predicted spurs' positions and                                   |

| amplitudes when (a) $f_{CH} = 2.404 GHz$ , (b) $f_{CH} = 2.426 GHz$                                            |

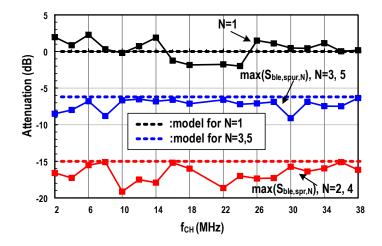

| Figure 3.5 Simulated fractional spur attenuation for different Ns                                              |

| Figure 3.6 Spectral mask for PLL spurious tones at frequencies <i>f</i> <sub>frac,N</sub> , N=1, 2, 3, 4, 5 to |

| satisfy BLE spectral mask                                                                                      |

| Figure 3.7 Block diagram of the proposed all-digital BLE-TX                                                    |

| Figure 3.8 Post-parasitic INL of 5 stage EMBTDC (left) and 45 stage DLTDC (right).                             |

| 44                                                                                                             |

| Figure 3.9 Behavioral simulation results of PLL (left) and BLE (right) output using (a)                        |

| DLTDC INL and (b) TSTDC INL with calibration at $f_{CH}$ =2.402GHz45                                           |

| Figure 3.10 (a) block diagram, (b) signal waveforms of TSTDC                                                   |

| Figure 3.11 Example of calibrating for delay between DCO_PH[1] and DCO_PH[2].      |

|------------------------------------------------------------------------------------|

| (a) Locking to DCO_PH[2] by adding EMBTDC_OFFSET, (b) illustration of 2            |

| cases that can happen due to random jitter                                         |

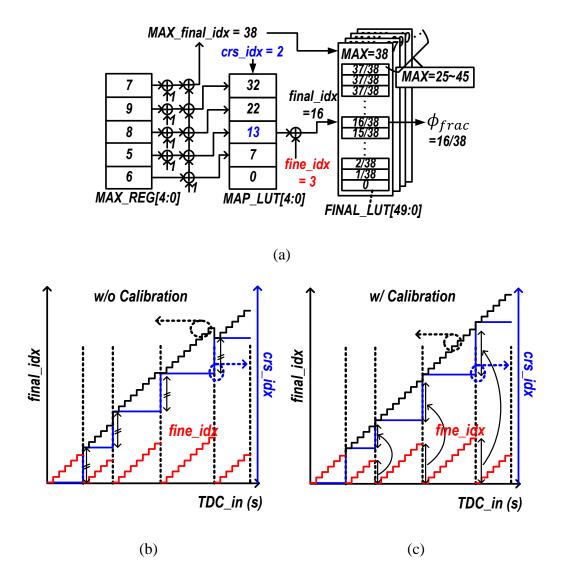

| Figure 3.12 Conceptual illustration of (a) process of generating MAP_LUT and       |

| FINAL_LUT and an example operation when crs_idx=2 and fine_idx=3, resulting        |

| TSTDC transfer function (b) without calibration assuming equal delay between       |

| DCO_PHs, (c) with proposed calibration                                             |

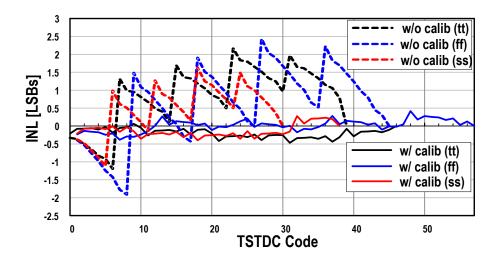

| Figure 3.13 VHDL simulation result of TSTDC with and without proposed calibration. |

| INL values of Figure. 13 are used for EMBTDC and DLTDC                             |

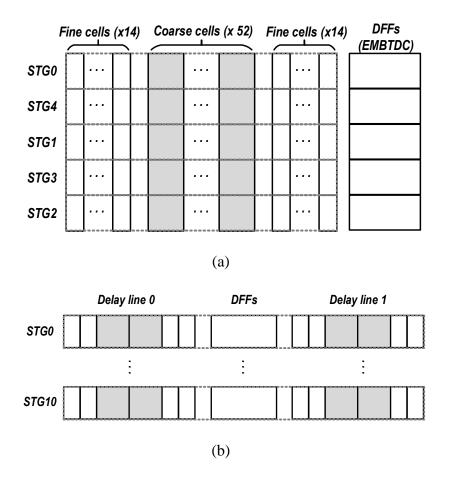

| Figure 3.14 Placement pattern for (a) DCO + EMBTDC and (b) DLTDC 53                |

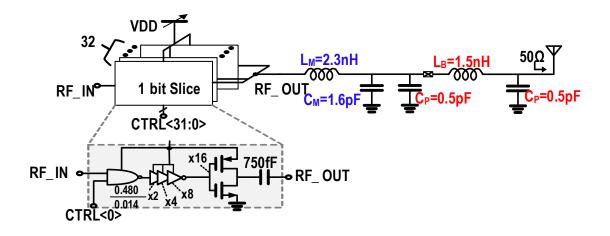

| Figure 3.15 Block diagram of the SCPA                                              |

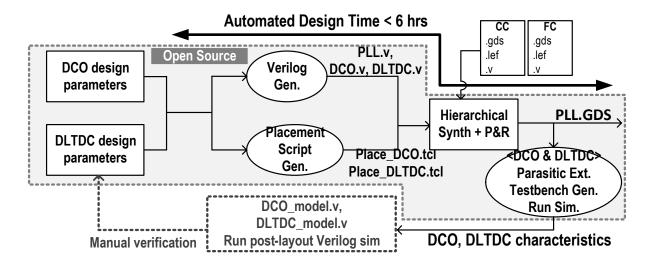

| Figure 3.16 Automated design flow for the PLL                                      |

| Figure 3.17 Automated design flow for the PLL                                      |

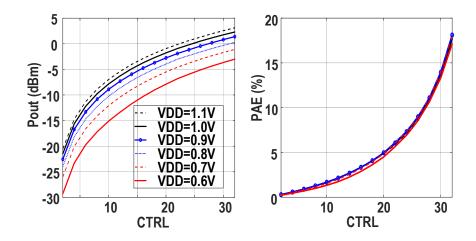

| Figure 3.18 Measurement results of SCPA. (a) Pout , (b) PAE with respect to CTRL   |

| and VDD                                                                            |

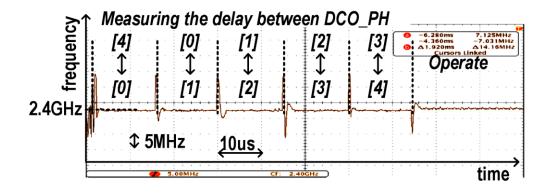

| Figure 3.19 Measurement results of standalone PLL Frequency vs time plot during    |

| calibration phase                                                                  |

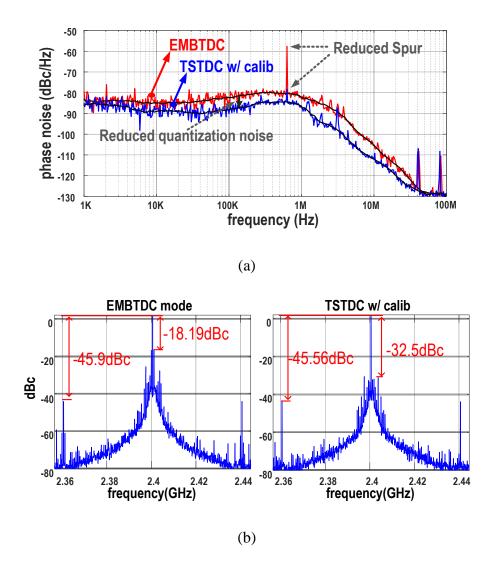

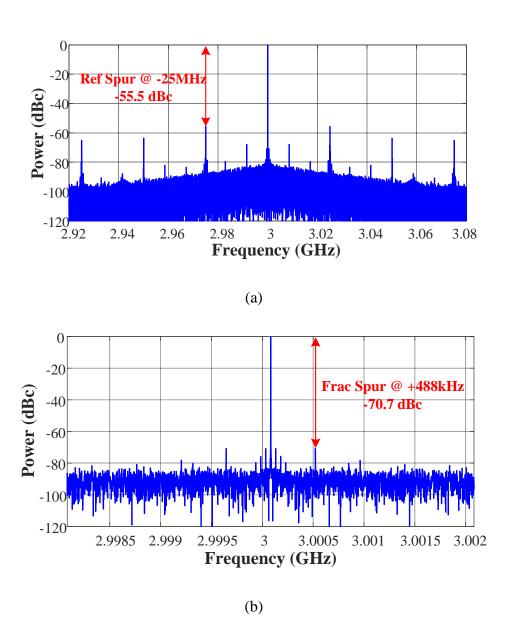

| Figure 3.20 Measurement results of standalone PLL. (a) phase noise plot and (b)    |

| spectrum for 2 different modes with FCW = 60.0156, FREF=40 MHz,                    |

| FOUT=2.4006 GHz                                                                    |

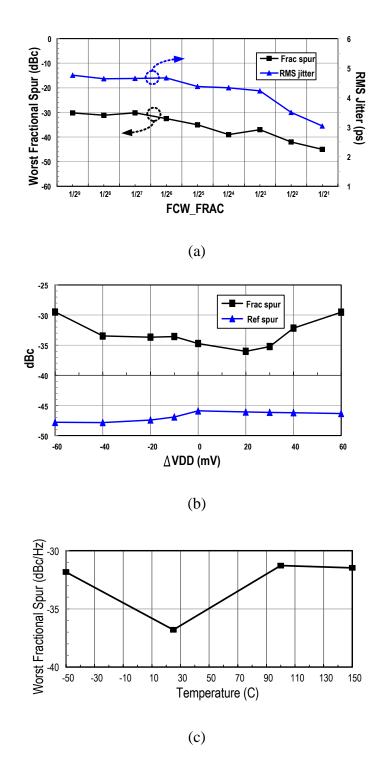

| Figure 3.21 (a) Measured worst-case fractional spurs and RMS jitters for different |

| FCW FRACs. (b) worst spurs for FOUT=2.40078 GHz for different VDD levels.          |

| (c) Simulated fractional spur levels depending on temperature for FOUT=2.40078                |

|-----------------------------------------------------------------------------------------------|

| GHz60                                                                                         |

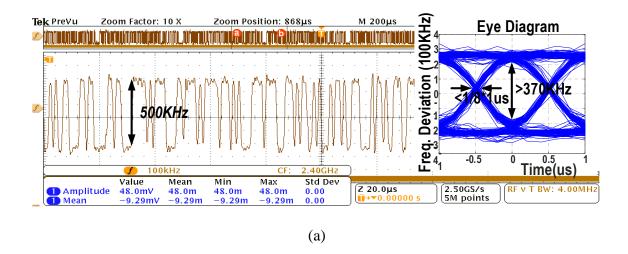

| Figure 3.22 Measured BLE performance. (a) frequency vs time plot with eye diagram,            |

| (b) GFSK spectrum comparison between different modes                                          |

| Figure 3.23 Measured PLL spectrum (left) and BLE spectrum (right) for fCH=2.452               |

| GHz along with spur prediction from Section II                                                |

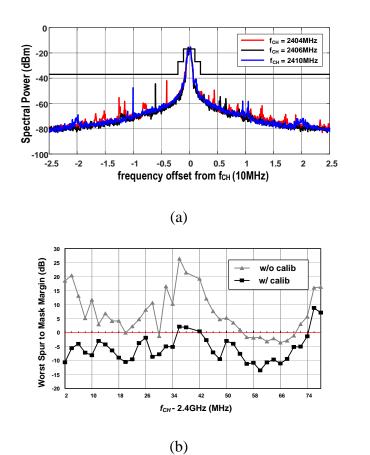

| Figure 3.24 Measured BLE (a) spectrum for 3 different channels, (b) worst case spur           |

| margin to the spectral mask across BLE channels w/ and w/o calibration 62                     |

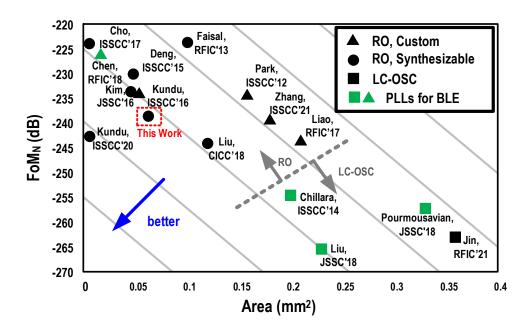

| Figure 3.25 FoM <sub>N</sub> and Area comparison                                              |

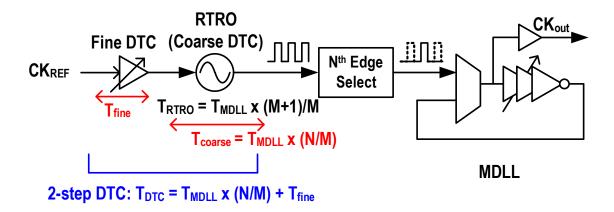

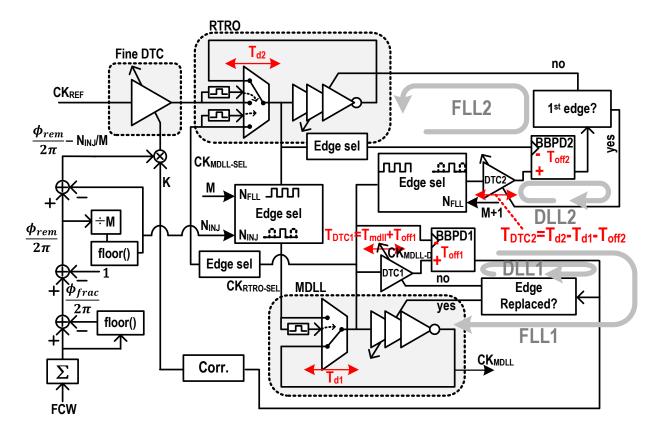

| Figure 4.1 Proposed 2-step DTC using RTRO                                                     |

| Figure 4.2 Block diagram of the proposed fractional-N MDLL                                    |

| Figure 4.3 Timing diagram of major signals for edge replacement, FLL1/2, DLL1/2.69            |

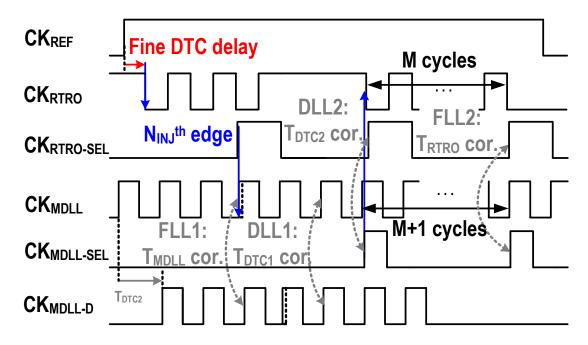

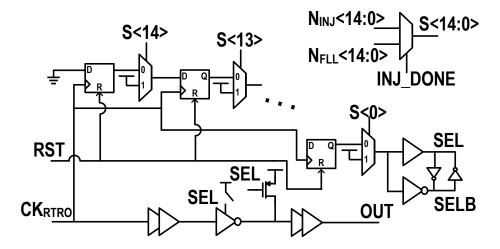

| Figure 4.4 Block diagram of (a) main MDLL and (b) RTRO                                        |

| Figure 4.5 Block diagram of RTRO edge selection block                                         |

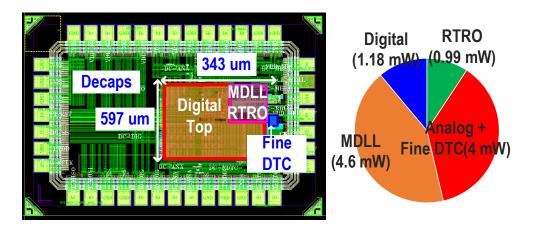

| Figure 4.6 Layout (left) and simulated power breakdown (right) of the proposed design.        |

|                                                                                               |

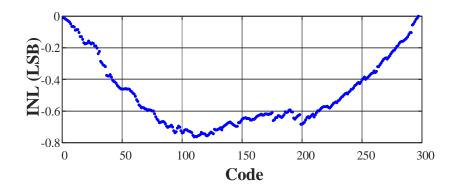

| Figure 4.7 Simulated INL of the fine DTC                                                      |

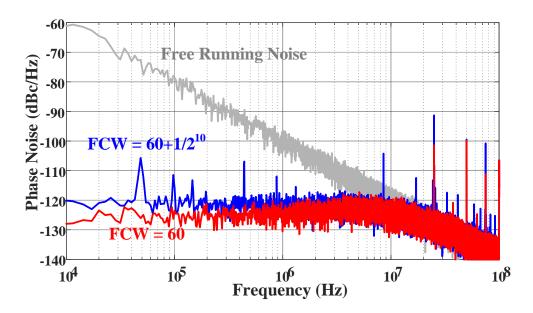

| Figure 4.8 Simulated phase noise performance of fractional-N operation (blue) and             |

| integer-N operation (red) and free-running mode (gray)                                        |

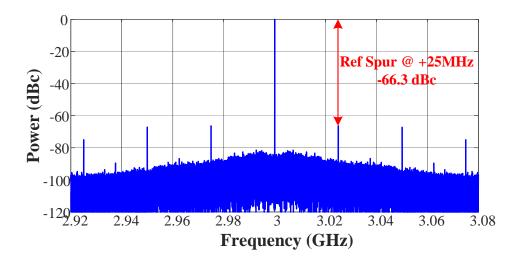

| Figure 4.9 Output spectrum of MDLL when FCW is 60                                             |

| Figure 4.10 Output spectrum of MDLL when FCW is 60+1/2 <sup>10</sup>                          |

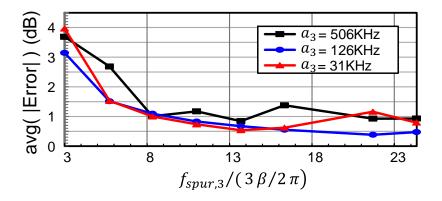

| Figure 6.1 Average error between (19) and (20) with respect to fspur, $33\beta2\pi$ ratio for |

| different a3. values                                                                          |

# **List of Tables**

| Table 2.1 I | DCO model accuracy for 125 designs compared to simulation results 13    |

|-------------|-------------------------------------------------------------------------|

| Table 2.2 S | Spec comparison between simulation and measurement                      |

| Table 3.1   | Performance summary and comparison with state-of-the-art fractional-N   |

| ADPLI       | Ls63                                                                    |

| Table 4.1 H | Block specifications from transistor-level post parasitic simulation 74 |

| Table 4.2   | Comparison with recent frequency synthesizers with DTC range (DR)       |

| reduction   | on technique77                                                          |

#### **Abstract**

As semiconductor fabrication process become complex to achieve target yield and performance in sub-20nm field-effect transistors (FETs), not only the number of design rule constraints (DRCs) exploded, but also the dependencies between different rules increased, which made manual layout design of custom chip more challenging and time consuming. While digital circuit design has been highly automated thanks to its better immunity to layout parasitic and mismatches, analog circuit design automation lags due to its layout sensitivity. As a solution for analog design automation, using standard digital flow to build a cell-based architecture has been suggested as one of few possibilities. This approach simplifies the design parameters to number of series/parallel cells from conventional width/lengths of every transistor, simplifying the modeling process. Also, it takes advantage of existing layout design engines that can handle complex DRCs, reducing one big step of design automation.

Among analog circuits, clock generators have been extensively explored in the area of cell-based architecture due to the digital nature of clock signal and early development of all-digital architectures. But prior arts showed limits in two areas: 1) fully automating the design process starting from a user given specification, 2) systematic solution to alleviate the degradation of analog performance due to the automatic routing.

In this dissertation, we propose an automated design flow for all digital phase locked loops (ADPLL) and architectural improvements including digital calibration scheme to push the performance limits of synthesizable clock generators. In chapter 2, design automation flow for baseline ADPLL architecture and novel feedforward scheme that doesn't require gain calibration is proposed. By combining physics-based equation and simulation results, we show a sample efficient (3 sets of simulation required) modeling method that successfully predicts key metrics of

digitally controlled ring oscillator (DCO) with error rate less than 1.5%. A prototype design was fabricated in 65nm process using the automation flow. We also propose a feedforward technique that selects the closest edge to the reference clock among interpolated DCO edges. This technique is amenable to PnR tool and reduces the jitter by 4.22x when the DCO noise dominates the TDC quantization noise.

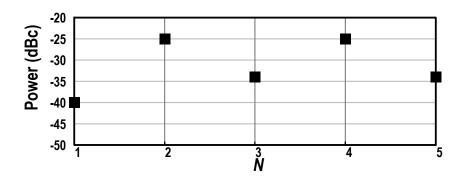

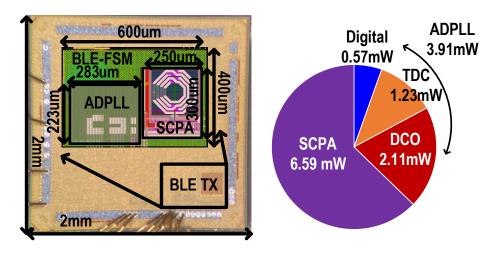

Chapter 3 analyzes PLL fractional spur's impact on Bluetooth low energy (BLE) spectrum to define spectral mask for PLL that can satisfy that of the BLE. Also, we propose a novel two-step TDC architecture and calibration scheme to overcome the performance limits coming from random routings. The 1.8-2.7 GHz PLL was fabricated in 12nm FinFET technology, consuming 3.91 mW at 2.4006GHz achieving FoM of -220.7dB in fractional-N operation.

Finally, chapter 4 proposes an all-digital fractional-N multiplying delay locked loop (MDLL) that uses reference triggered ring oscillator (RTRO) as a coarse DTC that reduces fine DTC range by 9x. Prototype design was fabricated in 65nm CMOS process and measured integer-N result shows 325 fs jitter and 16.1mW power consumption, achieving FoM of -237.7 dB. Simulated fractional-N operation shows worst case fractional spur of -41.9 dBc and rms jitter of 507 fs.

## **Chapter 1 Introduction**

#### 1.1 Increasing Demand for Analog Design Automation in sub-20nm Technology

With ever-increasing demand for small and fast computers for deep learning and Internet of Things (IoT), chip fabrication industry brought commercialized transistor length down to 3nm. While this significantly improved computational power, it posed new challenges to circuit designers; the exponentially increased DRC rules complicates the manual layout design. To ensure manufacturability in such small scale in the presence of variation, edge placement error and variety of other issues, the DRC rules have grown drastically as shown in Figure 1.1 [1]. Dependencies between different rules complicates the design process even more. Some examples of restriction in finFET technologies are uniform width and pitch to reduce non-ideal lithographic effect, unidirectional orientation, double coloring, and gridded design [2]. These restrictions require designers to use patterned and segmented layout styles rather than conventional "analog style" layout, reducing the merit of custom layout compared to auto-PnR layout. Also, the complex DRC significantly increases the manual design time.

Solutions for analog circuit layout automation that are suggested to reduce the time-to-market of chip design industry can be categorized into two streams: 1) automation from the substrate level [3], [4] and 2) cell-based approach utilizing existing digital PnR tool [5]–[10]. The first method develops a software that automatically generate a DRC clean Graphic Design System

Figure 1.1 Trend of DRC rules and operations [1]

(GDS) for every layer in the PDK with given design rules and user directives. For advanced technology, a grid-based routing has been adapted to handle complex DRC rules with better portability. It successfully mimics the shape of conventional analog layout and achieves similar mismatch and parasitic performance with a manually designed one. But some manual effort of modifying the process-specific primitives when porting to a new process is required to implement a DRC/LVS clean layout. Also, generating a design for a given user specification requires a transistor-level solution searcher, which complexity increases exponentially with the number of transistors. While many research use machine-learning (ML) based model for schematic optimization [3], [4], the amount of training data required for modeling a large-scale analog circuit limits its practical usage due to the enormous number of simulations required. The second approach, on the other hand, uses cell-based architectures which design parameters are simple integer values (number of series/parallel cells) and therefore, simplifies the modeling process with or without ML model. Also, by taking advantage of the built-in PnR engine of digital layout tool, the cell-based approach has minimum porting cost if the unit cells are prepared. But the resulting

analog performance suffers from increased mismatches and parasitic due to random placements and routings.

In Chapter 2, design automation flow for synthesizable ADPLL is presented which requires only 3 sets of simulation results to make a model and takes <1.2 hours to generate a GDS from a given input specification. Also, a novel feedforward scheme that doesn't require gain calibration is proposed in the synthesizable PLL and its effect and limitations are analyzed. The analysis is compared to the measured results from a chip fabricated in TSMC 65nm.

#### 1.2 Next Step for Synthesizable Phase Locked Loops

The PLL is one of the most popular building blocks being explored with the cell-based methodology for its early development of all-digital architectures and the digital nature of a clock signal [11]–[27]. The first generation of synthesizable PLLs focused on the cell-based implementations for integer-N operation. [11] proposed a tri-state inverter based DCO, [12] added a pulse-width modulation on the enable signal of the DCO cell to achieve higher frequency resolution. But the jitter power trade-off was inferior compared to manually designed integer-N PLLs, resulting in FoMs worse than -219 dB.

The second phase of the research explored fractional-N operation with aggressive noise suppression through edge replacement architectures such as injection-locked PLLs (ILPLL) [13], [17], [23], [26] and MDLLs [16], [19], [20]. While the best FoMs achieved are -247.2 dB for integer-N [18] and -234.4 dB for fractional-N [23], designs with FoM < -227dB have frequency multiplication ratios under 25 as shown in Figure 1.2. This limits the practical usage for higher frequency applications such as multi-gigahertz wireless communication circuits without using expensive high frequency crystal oscillators.

Figure 1.2 FoM and frequency multiplication ratio of published synthesizable PLLs

A PLL for a multi-gigahertz wireless transmitter is a good next target for cell-based PLL designs. For example, the BLE specifications require the 2.4GHz GFSK signal to have an eye-opening greater than 370KHz for 1Mbps data rate and spurious emission to be under the spectral mask. Random routing from a P&R tool increases delay mismatches in multi-stage timing control blocks such as the DCO, TDC and DTC, resulting in a high fractional spur due to the nonlinearity. The high bandwidth required for the data rate and RO noise suppression combined with this nonlinearity poses a challenge for synthesizable PLLs to meet the spectral mask of the BLE specification. A systematic solution for the problem is required to maximize the strength of short design and porting time of synthesizable circuits.

In Chapter 3, two-step TDC architecture is proposed as part of synthesizable ADPLL for BLE-TX in order to overcome the resolution limit of the baseline TDC. Also, a calibration scheme that alleviates coarse TDC nonlinearity caused by random routing is presented. The design was fabricated in GLOBAL FOUNDRY 12nm FinFET process and the 1.8-2.7 GHz PLL consumes

3.91 mW at 2.4006GHz achieving FoM of -220.7dB in fractional-N operation. Measured performance satisfies BLE standard requirements thanks to the proposed techniques.

### 1.3 Need for Low-Jitter Frequency Synthesizers

While ring oscillator (RO) has shown its potential of replacing some applications such as BLE that inductor-capacitance (LC) oscillator was conventionally used in, high data rate wireless communication systems still require LC oscillators to satisfy the stringent jitter requirements. For example, 5G communication system requires integrated phase noise (IPN), which is equivalent to error vector magnitude (EVM) in 4<sup>M</sup> QAM scheme [28], less than -35 dBc, which translates to RMS jitter of 404 fs for 7 GHz. Also, fractional-N synthesizers are preferred for its ability to generate fine-spaced carriers, which varies between 15 kHz – 450 kHz for 5G, with a fixed reference clock, which typical range is 10-100 MHz. Therefore, pushing the limit of jitter

Figure 1.3 Jitter vs EVM plot for 5G communication system in FR1 band (<7GHz)

performance of RO-based fractional-N frequency synthesizers is the key next step to broaden its application.

Edge replacement circuits such as IL-PLL and MDLL are inherently excellent at suppressing DCO phase noise thanks to the large effective bandwidth achieved by the noise-resetting action every reference cycle [29]. In Chapter 4, a fractional-N MDLL that uses RTRO as a coarse DTC has been proposed. Fabricated in 65nm CMOS technology, it achieves RMS jitter of 325 fs for integer-N operation at 3.25 GHz. Simulated fractional-N operation shows RMS jitter of 353 fs with worst case fractional spur of -53 dBc.

#### 1.4 Thesis Contributions

In summary, this dissertation proposes a design automation flow for PLL that is highly portable to reduce the time-to-market of IC industry amidst an exponentially increasing design complexity. Also, we present digital frequency synthesizer architectures that alleviates the analog issues caused by the automated routing, or pushes the performance limit of RO-based synthesizer. The automation flow only requires 3 sets of simulation results to generate a highly accurate model of error rate less than 1.5% that predicts the PLL performance and 8 PLLs are generated and the performances are compared to the input specifications to demonstrate the flow. Next, a fully-synthesized PLL in a BLE-TX with novel two-step TDC architecture and calibration scheme to reduce the PnR induced nonlinearity is proposed and analyzed. The measurement results satisfy the BLE requirements thanks to the proposed techniques. Finally, an all-digital fractional-N MDLL that uses RTRO as a coarse DTC to reduce the fine DTC range by 1/9 is proposed. Measured integrated jitter of integer-N operation is 325 fs, achieving FoM of -237.3 dB. Simulated fractional-N operation shows jitter of 507 fs, achieving FoM of -233.5 dB.

# Chapter 2 Design Automation of Synthesizable PLL and a Calibration-free Feedforward Technique

#### 2.1 Introduction

In this chapter, we present a synthesizable ADPLL generator that uses a simple analytical model for DCO characterization which only requires 3 sets of simulation results. Based on the DCO performance, PLL specifications are predicted by frequency-domain model using the known transfer functions of D-flip flop (DFF) based time to digital converter (TDC) and digital loop filter (DLF). The combination of human knowledge based model and existing digital synthesis tool incredibly fastens the process of characterization and design.

To prove the concept, 8 PLLs are generated from different input specifications in 65nm CMOS technology, and their performances are compared with the given requirements. One of the PLLs is fabricated as part of fully-synthesized SoC [5] and the measurement result is compared to the predicted values.

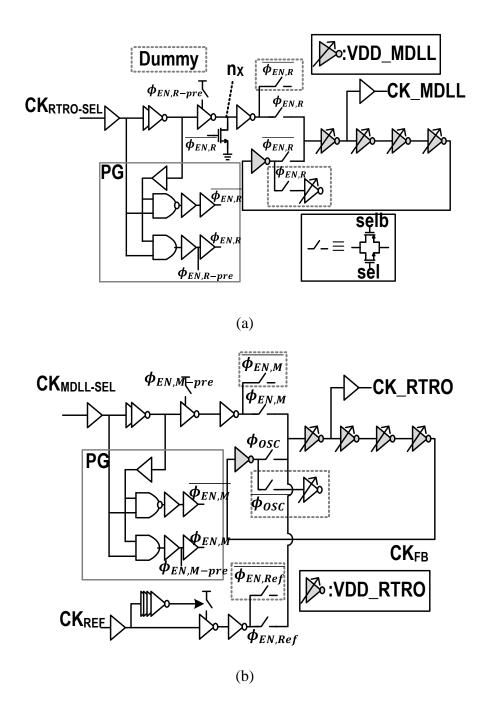

#### 2.2 Cell-based Architecture

We employ an embedded TDC (EMBTDC) [30] based phase-domain ADPLL architecture [31] and the simplified block diagram is shown in Figure 2.1. DCO's phase information is captured in

Figure 2.1 Fully-synthesizable ADPLL architecture and the modeling approach for Digital and Analog portion.

the form of digital words by EMBTDC and digital counter at the rising edge of reference clock, each generating fractional and integer phase information. Phase/frequency comparison is done in the digital domain by subtracting the accumulated phase information of DCO from that of the target phase. Target phase information is generated by accumulating the programmable frequency command word (FCW) every reference cycle. The phase error information is then processed through the digital loop filter and controls the DCO frequency to correct the phase/frequency error.

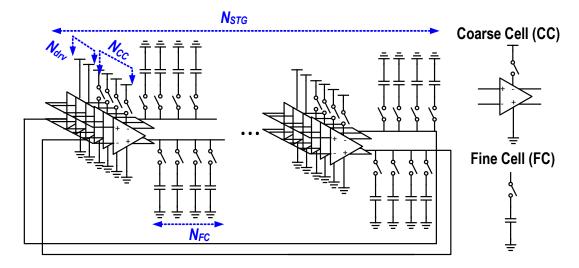

The DCO architecture is shown in Figure 2.2 and is composed of 2 custom-designed auxiliary cells (aux-cells): tri-state differential inverter (coarse controller: CC) and switched mosfet-capacitor (Fine controller: FC), which are digital standard cell grid compliant. As the name indicates, the former coarsely tunes the frequency while the latter tunes finely. The four design variables that determine the DCO performance are: 1. Number of tunable CC (N<sub>CC</sub>), 2.

Figure 2.2 Cell-based DCO architecture with its design variables and the 2 auxiliary cells.

Number of tunable FC ( $N_{FC}$ ), 3. Number of always-on CC ( $N_{DRV}$ ), 4. Number of stages ( $N_{STG}$ ), as shown in Figure 2.2. Depending on these design variables, the frequency range, nominal frequency, phase noise and power of the DCO varies. Detailed properties of operation will be discussed in the next section. The cell-based DCO can be laid out by a PnR tool, which enables the use of a standard digital flow for the whole PLL.

#### 2.3 Overall Design Automation Flow

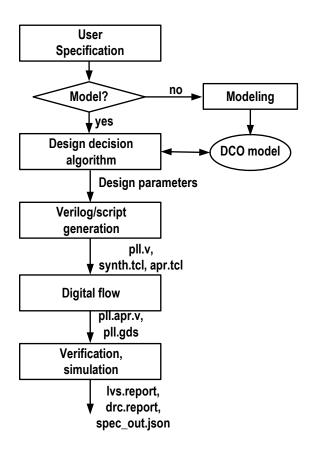

The overall automation flow is shown in Figure 2.3. The DCO modeling procedure is run in the absence of a model file. Generated model predicts the performance of the DCO and PLL from design parameters. Using the model, the design decision algorithm searches for the designs that satisfy the user given specifications. Once the design parameters are decided, Verilog source files and scripts for synthesis and PnR are generated. The tool then automatically runs the digital flow all the way through drc/lvs. Currently supported specifications are frequency range, nominal frequency, frequency resolution, DCO power consumption and in-band phase noise

Figure 2.3 Overall automation flow

level. As an open-source project this list of specifications is expected to grow with future contributions. Details of Modeling, Design solution searcher and implementation are explained in the following sections.

## 2.3.1 Modeling DCO and PLL

The objective of the modeling procedure is to generate a model that predicts the PLL performance for a pre-defined design space (currently 2.6M designs). The DCO performance determines not only the frequency range and resolution, but also the TDC quantization level since

an EMBTDC is employed. Therefore, the in-band phase noise level of the PLL can also be calculated for a given bandwidth and DCO specifications and the DCO model plays a key role in the overall PLL model. Since the transistor level behavior impacts the DCO specs, the model is built from SPICE simulations. These simulations are automatically run for several different DCO designs to capture the cell-level characteristics that impact the DCO-level specifications, without needing to know the physics-level parameters.

We use the analytical frequency equation proposed in [32] that uses PDK/aux-cell specific constants that represent the effective current to capacitance ratio for predicting the performance as a function of the aforementioned design parameters. The frequency of the DCO can be expressed as follows.

$$f_{dco} = \frac{N_{CC-on} + N_{DRV}}{((N_{CC} + N_{DRV}) \cdot \alpha + N_{SC} \cdot \beta + N_{SC-on} \cdot \gamma) \cdot N_{Stg}}$$

(1)

$$\alpha = C_{CC}/I_{CC} \tag{2}$$

$$\beta = C_{FC}/I_{CC} \tag{3}$$

$$\gamma = C_{FC-on}/I_{CC} \tag{4}$$

Where  $I_{CC}$  is the driving strength of CC,  $N_{CC-on}$  is the number of enabled CCs per stage,  $N_{DRV}$  is the number of always-on CC per stage,  $C_{CC}$  is the parasitic capacitance per CC,  $C_{FC-on}$  and  $C_{FC}$  are the capacitance of FC when it is on and off, respectively.  $N_{CC-on}$ ,  $N_{FC-on}$  are tunable values and used to change the frequency of the DCO during PLL operation. To acquire three constants  $\alpha$ ,  $\beta$  and  $\gamma$ , we need three simulation results with different design variables and tuning words. The modeling procedure automatically runs transient simulation for 3 different designs and extracts the constants by solving the equations. For the phase noise modeling of the DCO, we employ the analytical expression for ring oscillator's phase noise spectrum due to the transistor's white noise

presented in [8]. We extract a phase noise constant  $K_{pn}$  with a noise simulation of one DCO design, where the phase noise at a certain frequency offset  $f_{offset}$  is expressed as:

$$L(f_{offset}) = \frac{K_{pn}}{N_{CC-on} + N_{DRV}} \left(\frac{f_{dco}}{f_{offset}}\right)^2$$

(5)

Phase noise simulation is run by SPECTRE periodic noise simulation to extract the model constant  $K_{pn}$  for nominal frequency, which is the frequency when  $N_{CC-on} = N_{CC}/2$  and  $N_{FC-on} = N_{FC}/2$ , with  $f_{offset} = 1$ MHz. Using previously obtained  $\alpha, \beta$  and  $\gamma$ , we now know  $f_{dco}$  for a certain design and tuning word. So, using the  $L(f_{offset})$  from only one simulation result, we can calculate the phase noise model constant  $K_{pn}$ . To evaluate the accuracy of the model, the flow runs simulations for user-defined range of designs and reports the maximum error rate for all the specs. Table 1 shows the maximum error rate of the model predicted values compared to the simulation results for 125 DCO designs. The strength of the equation-based model is the sample efficiency, which requires only 3 sets of simulation results per PDK. For post layout performance, we assume  $\alpha, \beta$  and  $\gamma$  scale independently but constantly over different designs due to parasitic capacitance. The parasitic uncertainty is regulated by using an auto-generated placement scripts to place the DCO cells in a fixed pattern.

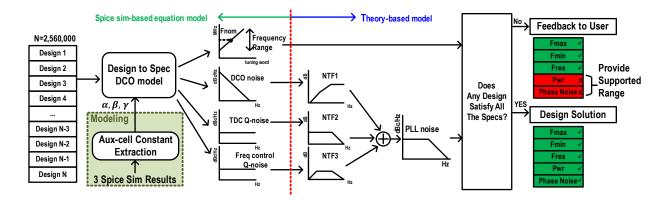

For PLL performance estimation, reference clock frequency and PLL bandwidth are assumed to be 10MHz and 1MHz, respectively. Since the bandwidth is programmable and the reference clock can be changed, the user can configure the dynamics of the output design as needed. The PLL in-band phase noise is estimated by applying noise transfer functions (NTFs) [33] to different noise sources based on model-predicted DCO specifications and adding them as shown in Figure 2.4. Assuming reference noise is negligible, we consider the noise sources: 1.

| Model Verification | Specifications |      |       |         |       |

|--------------------|----------------|------|-------|---------|-------|

|                    | Fmax           | Fmin | Fres  | PN@1MHz | Power |

| Max Error(%)       | 0.58           | 3.77 | 10.53 | 6.82    | 1.33  |

Table 2.1 DCO model accuracy for 125 designs compared to simulation results

DCO phase noise, 2. TDC quantization noise, which depends on the number of stages of the DCO, 3. Frequency control quantization noise, which depends on the frequency resolution of the DCO.

#### 2.3.2 Design Solution Searcher

This part of the tool searches for design solutions that satisfy user given specifications. This is done by sweeping a pre-defined design space with the model file and filtering the designs that satisfy the input specifications. Since the prediction through the model is simple mathematical calculations, it takes less than a minute to search 2.6M designs.

Finding a feasible set of specifications can be challenging from a user perspective. For example, DCO has a tradeoff between frequency, power consumption and phase noise. If the user requires a combination of the three specs that results in a figure of merit (FoM) better than the achievable value, no design will satisfy the given specifications. To give a sense of feasible ranges of specs to the user, the tool prints out the achievable range of specs for the failed categories if it cannot find a design that satisfies all the specs. This process is shown in Figure 2.4, where the tool provides a range of power consumption and Phase noise that are achievable so that the design solution can be met in the next iteration.

Figure 2.4 Design solution searching process with different modeling method for DCO-level and PLL-level. NTF1, 2, 3 are noise transfer functions from each noise source to the phase of the output clock. Q-noise indicates quantization noise.

#### 2.3.3 Back-End Flow

Once the design parameters are chosen, Verilog sources describing a particular PLL are generated automatically by changing the parameters of baseline Verilog files. The TCL scripts for digital flow are also generated correspondingly. Timing constraints and area of the design changes according to the nominal frequency of DCO and estimated area from the synthesis. To minimize the impact of layout on oscillator's performance, DCO is implemented separately with different power domain and used as a hard macro in the PLL layout. The placement of the DCO inside the PLL is described in a factorized number of core-size to ensure portability over designs and PDKs. Using the TCL scripts, digital flow is automatically run followed by a post-parasitic SPICE simulation of DCO to check its analog performance. Resulting DCO specifications are then used by a Matlab behavioral model to verify the PLL performance in a time-domain simulation and the results are written in a *spec\_out.json* file together with the input specs, allowing the comparison between the two.

#### 2.4 Design Examples and Measurement Results

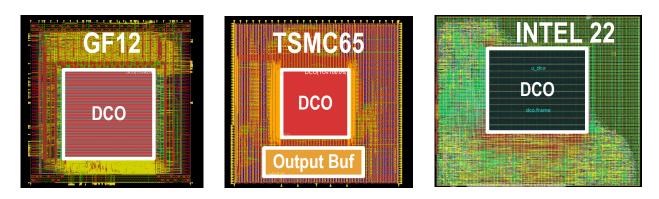

The tool currently supports GF 12nm, TSMC 65nm and Intel 22nm technology for PLL generation. Examples of the generated PLL layouts are shown in Figure 2.5. To show design flexibility, we generated 8 PLLs with random input specifications in 65nm process. Frequency range and nominal frequency are verified by post-pex SPICE simulation, while phase noise performance of the PLL is verified by Matlab time domain behavioral model using DCO performance extracted from analog simulation results. Figure 2.6 shows the input and output specifications. We can observe that the output frequency range is wider than the input, nominal frequency of input and output is approximate, while the output phase noise at 1MHz offset is lower than the required phase noise limit. As a prototype design, a PLL was fabricated and measured, which die photo is shown in Figure 2.7. Table 2.2 compares simulation results with the measured performance. Figure 2.8 shows the comparison between measurement, frequency domain model and simulation result of PLL phase noise at 840MHz with 20MHz reference clock and we can observe that the three high accuracy. agree in

Figure 2.5 Example layouts of PLLs in GF 12nm (left) and TSMC 65nm (right).

Figure 2.6 Performance comparison of 8 Generated PLL designs for different input specifications.

Figure 2.7 Die photo of the fabricated PLL as part of SoC in TSMC 65nm.

|           | Specifications |      |      |      |                |

|-----------|----------------|------|------|------|----------------|

|           |                |      |      |      | DCO Power (mW) |

| Sim       | 1065           | 209  | 643  | 11.1 | 7.2            |

| Meas.     | 940            | 190  | 558  | 11.5 | 6.9            |

| Error (%) | 11.73          | 9.09 | 13.2 | 3.7  | 4.16           |

Table 2.2 Spec comparison between simulation and measurement

Figure 2.8 Phase noise comparison between measurement, model and simulation results at 840MHz.

#### 2.5 Calibration-free Feedforward Noise Cancellation

One of the techniques to compensate the RO performance is feedforward noise cancellation (FNC) [1-2]. By feeding forward the phase error captured by the phase detector to the output clock, FNC reduces the noise level of the PLL without affecting the stability. Figure 2.9 shows 2 different architectures of previously published FNC PLLs. [34] uses a delay-line discriminator (DD) embedded in the RO to extract the out-of-band PN and cancels the noise component using a voltage-controlled delay (VCD) element outside of the PLL. [35] uses a sub-sampling phase detector (SSPD) to capture the phase error and uses its output voltage to control the VCD. Both [34] and [35] achieved >10dBc/Hz PN suppression with FNC. However, since the controllable delay unit that cancels the noise is separate from the noise detection unit, both require gain calibration of the FNC path for accurate cancellation. We propose an FNC method that does not require any calibration, and is amenable to cell-based design and APR.

## 2.5.1 Edge Selecting Feedforward Scheme

A block diagram of the proposed feedforward ADPLL is shown in Figure 2.10. The baseline architecture is adapted from [31]. The phase information of the DCO is captured by an embedded TDC [30] and digital counter. The reference phase ramp is generated by integrating the frequency command word (FCW). Phase comparison and filtering is done in the digital domain, clocked by the retimed reference clock. The DCO is composed of 8 stages of tri-state differential inverter cells and switched capacitor cells and is controlled by the output of the loop filter. The coarse and fine-tuning words each controls the number of tri-state cells and switched capacitors that are enabled per stage. An embedded TDC latches the node voltages of each stage of the DCO on the rising edge of the reference clock, capturing the fractional phase error. In our design, 8 differential phase interpolators double the 16 phases of the differential DCO. So, the TDC quantizes the fractional phase error into 5-bits.

Figure 2.11 shows a signal diagram of edge selection logics. Initially, CLK\_OUT is connected to DCO\_phase[0], which was the last edge before CLK\_REF on the previous cycle. But on the next rising edge of CLK\_REF, due to DCO noise, DCO\_phase[3] is the last edge before CLK\_REF instead of DCO\_phase[0]. This information is captured by embedded TDC, latching DCO\_phase[3]=1 and DCO\_phase[4]=0. Using this information, the code of the edge selection block gets updated on the retimed CLK\_REF, which is approximately 4 DCO cycles after the reference edge. The edge selection block is composed of tri-state buffers from digital standard-cell library, functioning multiplexer as a clock that connects CLK OUT the

Figure 2.9 Timing diagram of the edge selection process

desired DCO edge. Now CLK\_OUT is connected to DCO\_phase[3], effectively reducing the phase error by  $3\Delta T_{tdc}$ , where  $\Delta T_{tdc}$  is the time resolution of the TDC.

One drawback of both the embedded TDC and the proposed FNC scheme is the quantization noise due to this finite time resolution of  $\Delta T_{tdc} = T_{dco}/N_{tdc}$  where  $T_{dco}$  is the period of the DCO clock, and  $N_{tdc}$  is the number of phases that the TDC latches (32 in the proposed design). The TDC resolution adds quantization noise into the loop and the FNC path, degrading the PN performance of the PLL.

#### 2.5.2 Linearized Noise Analysis

Figure 2.12 illustrates a linearized phase domain model of the proposed PLL with different noise sources. The term main path (MP) and FNC path (FNCP) will be used to indicate the normal PLL loop and the feedforward path.  $\phi_{pll_{out}}$  is the output phase of MP, which is sampled by the reference clock on every phase comparison event. In the frequency domain, this generates a train of copied spectra with  $f_{ref}$  spacings (red graphs). The loop filter in the MP suppresses

Figure 2.10 Linearized phase domain model for the proposed PLL

these copied spectra while the FNCP only has filtering by zero-order hold (ZOH) action, which transfer function is

$$H_{ZOH}(f) = e^{-i\pi f T_{ref}} sinc(f T_{ref})$$

(1)

Where  $T_{ref} = 1/f_{ref}$ . Since  $H_{ZOH}(s)$  has  $1/f^2$  roll off, it suppresses the out-of-band spectra, but not as sharp as the MP does, which transfer function is

$$H_{OL}(f) = \left(K_p + \frac{K_i}{1 - z(f)^{-1}}\right) \cdot z(f)^{-1} \cdot H_{ZOH}(f) \cdot \frac{K_{DCO}}{1 - z(f)^{-1}}$$

(2)

Where  $z(f)^{-1} = exp(-i2\pi f/f_{ref})$ . Based on (1) and (2), bellow three sections will analyze the FNC effect on different noise sources.

#### 2.5.2.A DCO noise shaping

In the following analysis, DCO noise implies the sum of 1) DCO random noise,  $\phi_{DCO,n}$ , 2) DCO phase deviation due to supply noise,  $\phi_{SUP,n}$ , and 3) DCO phase deviation due to DCO frequency resolution,  $\phi_{\Delta f_{DCO,n}}$ .  $S_{\phi,DCO,n}(f)$  indicates the noise spectrum of DCO noise. The PN spectrum of the PLL output due to DCO noise is then expressed as

$$S_{\phi,MP}(f)|_{DCO,n} = S_{\phi,DCO,n}(f) \cdot \frac{1}{1 + H_{OL}(f)}$$

(3)

The copied spectra generated from sampling action are not correlated with  $\phi_{pll_{out}}(f)$ . Thus, the FNCP adds uncorrelated noise shaped by  $|H_{ZOH}(f)|^2$  while cancelling the correlated portion shaped by  $|1 - H_{ZOH}(f)|^2$  [6]. Sum of the two is expressed as

$$S_{\phi,FNCP}(f)|_{DCO,n} = |1 - H_{ZOH}(f)|^2 \cdot S_{\phi,MP}(f)|_{DCO,n}$$

$$+ |H_{ZOH}(f)|^2 \cdot \sum_{\substack{k = -\infty \\ k \neq 0}}^{\infty} S_{\phi,MP}(f - k \cdot f_{ref})|_{DCO,n}$$

(4)

Because the high frequency suppression of  $|H_{ZOH}(f)|^2$  is less sharper than  $|H_{OL}(f)|^2$ , FNCP adds out-of-band noise to the MP. Figure 2.13(a) and (b) show a PN break-down of MP and FNCP, showing this DCO noise shaping of both paths. But the amount of noise cancelled by the FNCP is much larger than the added, reducing the overall jitter from DCO and power supply.

## 2.5.2.B TDC quantization noise shaping

as

Assuming white noise, the single-sided TDC quantization noise spectrum can be expressed

$$S_{\phi,TDC,n}(f) = \frac{(2\pi)^2}{12} \left(\frac{\Delta T_{TDC}}{T_{DCO}}\right)^2 \frac{1}{f_{ref}}$$

(5)

The PN spectrum of MP due to TDC quantization is then expressed as

$$S_{\phi,MP}(f)|_{TDC,n} = S_{\phi,TDC,n}(f) \cdot \frac{H_{OL}(f)}{1 + H_{OL}(f)}$$

(6)

The spectrum of TDC noise at node *preFNC* is then

$$S_{\phi,preFNC}(f)\big|_{TDC,n} = S_{\phi,TDC,n} \cdot \frac{1}{1 + H_{OI}(f)}$$

$$\tag{7}$$

The transfer function of the correlated path of FNCP for  $S_{\phi,MP}(f)|_{TDC,n}$  is then

$$\frac{\phi_{FNCP,corr.}}{\phi_{MP}|_{TDC,n}} = \left|1 + \frac{H_{ZOH}(f)}{H_{OL}(f)}\right|^2 \tag{8}$$

Unlike the transfer function of the DCO's correlated path in (4), (7) adds noise instead of cancelling it. Intuitively, since  $S_{\phi,preFNC}(f)|_{TDC,n}$  is a high-passed spectrum of  $S_{\phi,TDC,n}(f)$ , the in-band correlated noises are not being cancelled as (4). For the uncorrelated noise, the transfer function is same as that of (4). Therefore, the FNCP increases the out-of-band noise as shown in Figure 2.13(a) and (b), while not cancelling the in-band portion. The total PN spectrum of FNCP from the TDC noise is

$$S_{\phi,FNCP}(f)|_{TDC,n} = \left| 1 + \frac{H_{ZOH}(f)}{H_{OL}(f)} \right|^2 \cdot S_{\phi,MP}(f)|_{TDC,n} + |H_{ZOH}(f)|^2 \cdot \sum_{\substack{k = -\infty \\ k \neq 0}}^{\infty} S_{\phi,MP}(f - k \cdot f_{ref})|_{TDC,n}$$

(9)

#### 2.5.2.C Total noise

Remaining noise source is the reference noise. Using the same principle as (4), the output PN spectrum of MP and FNCP due to reference noise can be written as

$$S_{\phi,MP}(f)|_{REF,n} = S_{\phi,REF,n}(f) \cdot \left| \frac{N \cdot H_{OL}(f)}{1 + H_{OL}(f)} \right|^2 \tag{10}$$

$$S_{\phi,FNCP}(f)|_{REF,n} = |1 - H_{ZOH}(f)|^2 \cdot S_{\phi,MP}(f)|_{REF,n}$$

$$+ |H_{ZOH}(f)|^2 \cdot \sum_{\substack{k=-\infty \\ k \neq 0}}^{\infty} S_{\phi,MP}(f - k \cdot f_{ref})|_{REF,n}$$

(11)

Where N is the frequency command word. The contribution from reference clock in the proposed design has <-8dBc/Hz contribution on the output noise compared to that of DCO or TDC. Therefore, the foregoing analysis assumes that the DCO random noise and TDC quantization noise are the only noise sources contributing to the output spectrum. The total noise of FNCP is approximately the sum of (4) and (9), which is

$$S_{\phi,FNCP}(f) = S_{\phi,FNCP}(f)|_{TDC,n} + S_{\phi,FNCP}(f)|_{DCO,n}$$

(12)

As observed from Sections II.B and II.C, FNCP reduces the overall noise contribution from DCO but increases the contribution from TDC. Therefore, the effect of FNC on the total noise performance depends on the relative levels of the two noises. When DCO noise dominates MP PN

as in Figure 2.13(a) and (c), FNCP reduces the overall noise level. This can be understood intuitively in the time domain. As shown in (c), when random jitter of MP output is much larger than the resolution of FNC correction, the abrupt phase corrections hide inside the random jitter, improving the jitter performance. When TDC noise dominates, however, the correction of FNCP outlies the random jitter, adding more noise to the MP as shown in Figure 2.13(d). In the frequency domain, this appears as an increase in the out-of-band noise from TDC, as shown in Figure 2.13(b). Figure 2.14(a) shows a contour plot of the relationship between the jitter ratio of two modes,  $\sigma_{rms,MP}/\sigma_{rms,FNCP}$ , and the in-band PN level of MP due to DCO and TDC noise. The jitter values are results of behavioral simulation with  $f_{ref} = 40MHz$ ,  $f_{out} = 840MHz$ , BW = 2.8MHz, sweeping  $\Delta T_{TDC}$  and DCO noise level (assuming  $1/f^2$  degradation). We can observe that the FNC has more effect with larger noise contribution from DCO and less from TDC. The difference should be approximately 10dBc/Hz or greater for FNC to have more than 1.5x of improvement. Since  $\Delta T_{TDC} = 1/(f_{DCO} \cdot 4 \cdot N_{stg})$  ), we can derive a condition of delay per DCO stage  $(\Delta T_{stg})$ which FNC is beneficial by 1.5x. Noise performance of the DCO will be characterized by  $FoM_{PN}$ , which is

$$FoM_{PN} = 10 \log_{10} \left( S_{\phi,DCO,n} \left( f_{off} \right) \cdot \frac{P}{1mW} \cdot \left( \frac{f_{off}}{f_{DCO}} \right)^2 \right) \tag{13}$$

where  $f_{off}$  is the frequency offset from  $f_{DCO}$  and P is the power consumption. Assuming  $S_{\phi,MP}(f_{BW})|_{DCO,n} = S_{\phi,DCO,n}(f_{BW})$ , where  $f_{BW}$  is the PLL bandwidth, by combining  $S_{\phi,MP}(f_{BW})|_{DCO,n} > 10 \times (5)$  with  $f_{DCO} = 1/(\Delta T_{stg} \cdot N_{stg})$ , the condition of  $\Delta T_{stg}$  for  $\sigma_{rms,MP}/\sigma_{rms,FNCP} > 1.5$  is

$$\Delta T_{stg} < \sqrt{\frac{\frac{1mW}{P} \cdot \frac{f_{ref} \cdot 10^{\frac{F_0 M_{PN}}{10}}}{0.49 \cdot f_{BW}^2}} \tag{14}$$

It is notable that  $N_{stg}$  is cancelled. Figure 2.14(b) shows a contour plot of this condition assuming  $V_{dd}=1.2\,V$ ,  $f_{ref}=40MHz$ ,  $f_{BW}=2MHz$ , while sweeping  $FoM_{PN}$  and P of DCO. The restriction for FNC is stricter with DCO with better  $FoM_{PN}$  and power consumption.

Figure 2.11 Performance comparison of MP and FNCP in two different environments. PN plots when (a) DCO noise dominates, (b) TDC noise dominates. Time domain simulation plot when (c) DCO noise dominates, (d) TDC noise dominates

Figure 2.12 Contour plots of (a) jitter improvement by FNC with MP in-band PN level due to DCO on x-axis and TDC on y-axis, (b) required maximum delay per DCO stage for FNC to be 1.5x beneficial.

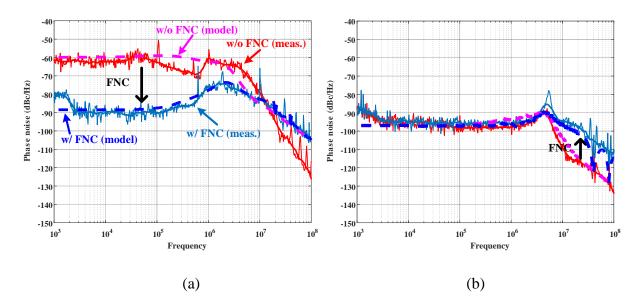

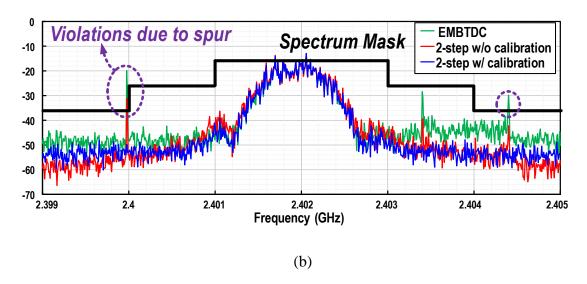

# 2.6 Synthesizable Feedforward PLL Measurement Results

A test chip was fabricated in 65nm CMOS technology. The layout of the PLL is done by APR tool, where the auxiliary cells are designed manually but then placed and routed automatically. The PLL is measured in two different modes: 1) High DCO noise, and 2) Low DCO noise. The two modes are realized by turning on or off a free-running RO that shares a supply with the DCO in the PLL. When the free-running RO is on, the supply noise due to its oscillation increases the noise level of the main DCO. For each environment, the phase noise plots with and without FNC are compared in Figure 2.15 along with the analytical model results. In the first case,  $f_{ref} = 20 \text{MHz}$ ,  $f_{out} = 800 \text{MHz}$ . From Figure 2.15(a), we can observe that FNC reduces the inband phase noise by 15 dBc/Hz at frequency offset of 1 MHz, and the integrated jitter (1 K - 10 MHz) by 4.22 x ( $291.8 \text{ps} \rightarrow 69.0 \text{ps}$ ), for only a 3.54 % increase in power ( $7.07 \rightarrow 7.32 \text{ mW}$ ). On the second case with low DCO noise,  $f_{ref} = 40 \text{MHz}$ ,  $f_{out} = 840 \text{MHz}$  and the power increased

Figure 2.13 Measured phase noise (meas.) in comparison with the analytical model (model) when (a) DCO noise dominates and (b) TDC noise dominates.

from 8.78mW to 9.05mW. As we can see from Figure 2.15(b), TDC quantization noise dominates the PLL noise and the FNC increases the out-of-band noise compared to the main path, increasing the integrated jitter (10.3ps  $\rightarrow$  18.6ps). The analytical model follows the overall tendency of the measurement results and accurately predicts both cases.

## 2.7 Conclusion

An automation flow for a synthesizable ADPLL has been proposed in this Chapter. The combination of human knowledge and simulation results fastened the modeling process to requiring only 3 sets of results. To prove the concept, 8 PLLs were generated, and their performances were compared to the input specifications. All output performances satisfied the input requirement and the phase noise prediction of behavioral model highly agreed with the measurement result. Also, a novel calibration-free feedforward implementation method for

synthesizable ADPLL is proposed as part of the fabricated chip. The effects of FNC depending on the dominant noise sources are analyzed with frequency domain model and the results are compared with measurements. The condition for the proposed FNC method to be beneficial is derived.

# Chapter 3 PLL Fractional Spur's Impact on FSK Spectrum and a Synthesizable ADPLL for a Bluetooth Transmitter

## 3.1 Introduction

The design and verification process is becoming more challenging for analog circuit designers due to the increased layout sensitivity and non-intuitive design rules from complex processes such as multi-patterning in sub-20nm nodes. Open-source analog generators (public cloud repositories for analog circuit design automation), have been developed over the past decade to assist analog circuit designers and reduce time-to-market of ASIC designs [5], [36], [37]. One of the approaches for automation is to adopt a cell-based analog circuit design and use existing digital synthesis tools to generate the layout [5]. By taking advantage of the built-in P&R engine in a digital layout tool, the cell-based approach has significantly lower porting cost once the cells are prepared.

While the PLL is one of the most popular building blocks being explored with the cell-based methodology, recent publications of cell-based PLLs focus on fractional-N frequency multipliers to widen the applications [13], [16], [17], [21]–[23]. While the automatic routing of the P&R tool is the biggest contribution to the reduced design time, it poses a new challenge in implementing a fractional-N PLL by adding mismatches in timing control blocks such as the

digitally controlled oscillator (DCO), TDC, and digital to time converter (DTC). Since the blocks process a saw-tooth shaped time error between the output and reference clock, their non-linearity over the range of at least one period of the DCO ( $T_{DCO}$ ) results in high fractional spurs in the output spectrum. While the blocks are widely used in fractional-N synthesizable PLLs, only a few ([16], [17]) proposed a systematic solution for the routing uncertainty.

[13] and [20] use the internal phases of the DCO to process fractional phase information.

[13] proposed a fractional-N injection-locked PLL (ILPLL) by injecting a reference edge to one of the interpolated internal phases of the DCO. A two-step DTC was introduced in [20] to delay the reference clock by a desired amount, where the internal phases of a replica DCO are used as coarse DTC steps so that the resolution is synchronized to the period of the main DCO. The DCO is especially vulnerable to routing mismatch since it requires a large number of cells and routing connectivity to cover a desired frequency range. While these architectures are highly sensitive to delay mismatch between DCO stages, both lack a circuit level solution for the problem.

[21] uses a direct-digital synthesizer driven by a free-running oscillator along with a D-flip-flop (DFF) based sub-sampling phase detector (SSPD). Fractional-N operation is achieved by adding a fractional code to the output of the SSPD. While the architecture alleviates the non-linearity coming from TDC/DTC by avoiding any D-to-A or A-to-D process during the phase error detection, the free-running oscillator and the phase interpolator are custom designed, degrading the merits of a synthesizable PLL. The PI is a source of non-linearity that directly impacts the output spectrum, which is very sensitive to the routing mismatch of P&R tool.

To solve the issue of routing mismatch in a two-step DTC, [16]–[18] compensate the coarse DTC's INL by setting proper offsets on the fine DTC control words for each coarse step. This zero-order interpolation-based calibration scheme systematically cancels a discontinuous INL

induced by the routing mismatches. However, the frequency command word (FCW) is limited to 10, which requires expensive reference clock with frequency ( $f_{ref}$ ) higher than 100s of MHz to support a multi-gigahertz output frequency.

In this chapter, we present an open-source, fully synthesizable PLL driven by a 40MHz reference clock for a 2.4GHz BLE-TX (FCW > 60) with a calibration scheme that compensates the P&R induced non-linearity [27], [38]. The proposed synthesizable ADPLL employs a novel two-step TDC (TSTDC) and digital on-chip calibration scheme that reduces the fractional spurs. An embedded TDC (EMBTDC) is used for coarse quantization and Vernier delay line TDC (DLTDC) is used for fine quantization. This reduces the required number of stages of DLTDC as well as its peak INL value, while it is used to measure and compensate the EMBTDC non-linearity. The BLE-TX was fabricated in 12nm FinFET technology and the measured performance satisfies the BLE standard requirements for most of the channels. The standalone PLL supports an output frequency range of 1.8-2.7GHz, consuming 3.91mW at 2.4006 GHz, occupying an area of 0.063mm<sup>2</sup>.

One of the major challenges of designing a PLL for BLE using a P&R tool is the degraded GFSK modulation performance caused by non-linearity which shows up as spurious tones in the frequency domain. To our knowledge, there is no existing analysis on the changes in the PLL fractional spurs before and during FSK modulation. In this work, we provide a detailed analysis of the PLL fractional spur's impact on the FSK spectrum and derive a spectral mask for PLLs that will then satisfy the BLE mask based on a semi-analytical model. Prediction of the BLE spectrum for a given PLL fractional spurs sets a clear linearity target for PLL designers and opens new possibilities for PLL designers to better optimize fractional-N PLLs for FSK modulation

applications, and explore architectures that are more easily ported and amenable to design automation.

# 3.2 Prediction of BLE-TX Spurious Tones from PLL Fractional Spurs

The center frequencies of BLE channels,  $f_{CH}$ , are 2MHz apart starting from 2.402GHz to 2.480GHz [39]. With  $f_{ref}>2$ MHz, a PLL needs to operate in a fractional-N mode in order to lock to a certain  $f_{CH}$ , and  $f_{ref}=40$ MHz is common for BLE transmitters. For data transmission, the PLL modulates the output frequency by +250kHz and -250kHz from  $f_{CH}$  for data 1 and 0, respectively. Spurious tones due to  $f_{CH}$  also are affected by this modulation, resulting in different positions and amplitudes in the FSK spectrum compared to those of a standalone PLL mode operating at  $f_{CH}$ . We investigate the effect of FSK modulation on spurious tones by defining the fractional spur positions due to different harmonics of periodic nonlinearity noise (PNN) of the PLL in Section II-A and using a mathematical model to derive the spurious tones' relative amplitudes and positions compared to the original values in Section II-B. Experimental results are shown in Section II-C to prove the derived model.

## 3.2.1 Fractional Spur Positions

Since the frequency modulation's effect of a fractional spur depends on which harmonic of the PNN that it originated from, we first need to relate each harmonic with the resulting fractional spur position. Unlike the case when the fractional frequency is realized by high-order

Figure 3.1 Phase Domain ADPLL block diagram with loop INL with respect to terr

multi-modulus dividers [40], [41], the fractional spur positions of a phase domain (PD) architecture [31] are more straight-forward to understand. As shown in Figure 3.1, in PD-PLLs, a saw-tooth shaped fractional phase error is processed by the TDC and digital loop filter. The loop nonlinearity with respect to the ideal time error between the PLL output clock  $CK\_DCO$  and reference clock  $CK\_REF$ , denoted as  $t_{err}$ , results in a PNN in the ensemble average of  $CK\_DCO$  frequency  $f_{DCO}$ , with a time period of  $(1/FCW\_FRAC) \cdot T_{ref}$ , where  $T_{ref}$  is the period of  $CK\_REF$  and  $FCW\_FRAC$  is the fractional part of the FCW. The discrete time saw-tooth shaped signal  $t_{err}$  can be expressed as

$$t_{err}[N_{ref}] = MOD(FCW\_FRAC \cdot T_{DCO}N_{ref}, T_{DCO}), \tag{1}$$

where  $N_{ref}$  is the current count of reference cycle,  $T_{DCO}$  is the period of  $CK\_DCO$ , and MOD(a, b) is a modulus function that returns the modulus value of a/b.  $t_{err}[N_{ref}]$  can be viewed as a sampled version of a continuous time (CT) signal with period  $(1/FCW\_FRAC) \cdot T_{ref}$  as shown in Figure 3.2(a). The CT PNN can be expressed in Fourier-series (FS) as

Figure 3.2 Conceptual illustration of (a) t<sub>err</sub>[N<sub>ref</sub>], (b) PSD of CT PNN, (c) time domain of DT PNN, (d) PSD of DT baseband PNN.

$$s_{CT}(t) = \frac{1}{2}a_0 + \sum_{N=1}^{\infty} a_N \cos(2\pi N f_{frac} t) + \sum_{N=1}^{\infty} b_N \sin(2\pi N f_{frac} t), N = 1, 2, 3 \dots$$

(2)

where  $f_{frac} = FCW\_FRAC \cdot f_{ref}$ . According to sampling theory, the baseband positions of the fractional spurs after being sampled at  $f_{ref}$  rate are the results of spurs at  $Nf_{frac}$  down converted by subtracting the nearest integer multiple of  $f_{ref}$ . Depending on which side of the closest multiple of  $f_{ref}$  that  $Nf_{frac}$  is, the spurious tone moves either closer or farther from the center frequency when  $FCW\_FRAC$  increases, which will happen during FSK modulation for transmitting data 1,

as shown in Figure 3.2(b) and (d). Thus, we define the fractional spur position of the N<sup>th</sup> harmonic of discrete time (DT) PNN as below

$$f_{spur,N} = N f_{frac} - a f_{ref}, a = 0, 1, 2, 3 \dots, \left(a - \frac{1}{2}\right) f_{ref} < N f_{frac} < \left(a + \frac{1}{2}\right) f_{ref}$$

(3)

For example, with  $f_{frac}$  =16MHz and  $f_{ref}$  =40MHz,  $f_{spur,2}$  = 40MHz - 32MHz = 8MHz,  $f_{spur,3}$  = 40MHz - 48MHz = -8MHz as shown in Figure 2.2(d) as the dotted arrows. While  $f_{spur,2}$  and  $f_{spur,3}$  are in same absolute frequency offset, when  $f_{frac}$  changes by  $\Delta f$ , frequency offset of  $f_{spur,2}$  reduces while it increases for  $f_{spur,3}$  as shown as solid arrows in Figure 2.2(d). The frequency perturbation due to the PNN is held for  $T_{ref}$  in PD ADPLL, allowing us to express the resulting sampled and held periodic signal by simply replacing  $Nf_{frac}$  of (2) with  $f_{spur,N}$  of (3), resulting in below equation. This definition will be used for the rest of the paper.

$$s(t) = \frac{1}{2}a_0 + \sum_{N=1}^{\infty} a_N \cos(2\pi f_{spur,N}t) + \sum_{N=1}^{\infty} b_N \sin(2\pi f_{spur,N}t), N = 1, 2, 3 \dots$$

(4)

# 3.2.2 Semi-analytical Model of BLE Fractional Spurs

In [42], the power spectral density (PSD) of a BFSK signal with random data was derived by obtaining an autocorrelation of the signal and then conducting a Fourier-transform. But the derivation assumes a spectrum without any spurious tone. By adding terms that mathematically represent PLL fractional spurs to the derivation, we analyze the impact of BFSK modulation on the spurious tones' positions and amplitudes and later prove that the maximum spur prediction is valid for GFSK modulation as well. This section shows a simplified version of the analysis while the details can be found in the Appendix. We assume  $a_0 = b_N = 0$  from (4) in this section, since  $a_0$  contributes only on the frequency offset, not the spurious tone, and the presence of  $b_N$  does not

change the result and the logical flow compared to only having  $a_N$ . Using the definition of frequency PNN in (4) and proper assumptions shown in the Appendix, a BFSK signal in the presence of fractional spurs can be written as

$$u_m(t) = A_u \cos \left( B_n(t) + \sum_{N=1}^{\infty} a_N \sin \left( C_{N,n}(t) \right) \right),$$

$$\approx A_u \cos \left( B_n(t) \right) - A_u \sin \left( B_n(t) \right) \cdot \left\{ \sum_{N=1}^{\infty} a_N \sin \left( C_{N,n}(t) \right) \right\}, \tag{5}$$

$$B_n(t) = 2\pi \cdot [f_{CH}t + x_{n+1}(250 \cdot 10^3)(t - nT) + (250 \cdot 10^3)\sum_{r=1}^n x_r], nT \le t < (n+1)T,$$

(6)

$$C_{N,n}(t) = 2\pi \cdot [f_{spur,N}t + x_{n+1}N(250 \cdot 10^3)(t - nT) + N(250 \cdot 10^3)\sum_{r=1}^{n} x_r], nT \le t < (n+1)T,$$

(7)

where  $x_n$  is the  $n^{\text{th}}$  transmitted data (1 or -1),  $B_n(t)$  and  $C_{N,n}(t)$  are the phase components due to the main signal and the fractional spur's  $N^{\text{th}}$  harmonic during frequency modulation for  $n^{\text{th}}$  data transmission, respectively.  $a_N$  is a scaled version of  $a_N$  to accommodate the frequency to phase conversion of PNN. We use phase terms instead of frequency terms because the phase information has to be preserved between two consecutive data transmission as a continuous phase FSK modulation. Illustration of the derivatives of  $B_n(t)$  and  $C_{N,n}(t)$ , which are the frequencies of each component, are shown in Figure 3.3. We can observe that  $B_n(t)$  deviates by 250kHz for data encoding while  $C_{N,n}(t)$  deviates by  $N \cdot 250$ kHz. The second term of (5) can be seen as a mixing between two signals:  $A_u sin(B_n(t))$  and  $\left\{\sum_{N=1}^{\infty} a_N \sin\left(C_{N,n}(t)\right)\right\}$ . Using sinusoidal properties, we can further expand the term as below.

$$A_{u}sin(B_{n}(t)) \cdot \left\{ \sum_{N=1}^{\infty} a_{N} \sin\left(C_{N,n}(t)\right) \right\}$$

$$= \sum_{N=1}^{\infty} \left\{ a_{N} \sin\left(B_{n}(t) + C_{N,n}(t)\right) + a_{N} \sin\left(B_{n}(t) - C_{N,n}(t)\right) \right\}. \tag{8}$$

As (8) shows, the mixing results in two terms per harmonic; addition between  $B_n(t)$  and  $C_{N,n}(t)$ , and subtraction between the two. For N=1, the second term of (8) leads to a single tone at  $f_{CH}-f_{spur,1}$  because both  $B_n(t)$  and  $C_{1,n}(t)$  have identical frequency modulation of 250kHz and they cancel each other. This can be applied to GFSK signal as well because the modulation terms are still identical for center frequency and the fundamental harmonic of the spurious tone.

Except for the second term of N=1, other terms of (8) can be seen as separate FSK signals with different center frequencies and frequency deviations. The first term of N=1 and both terms of other odd harmonics (N=3, 5, 7...) result in phase accumulation of integer multiples of  $\pi$  for

Figure 3.3 Conceptual illustration of the impact of modulation on fractional spurs of equation (8).

one data period (1*us*), which is expressed as  $2\pi \cdot (N \pm 1) \cdot 250kHz \cdot 1us$ . In these special cases, continuous phase FSKs become identical to discontinuous FSKs because every data transmission ends with the same phase. The spectrum of discontinuous phase modulation contains two sinusoidal functions with amplitude degraded by 6.02 dB compared to the original signal and located at  $\pm \Delta f$ , where  $\Delta f$  is the frequency deviation for data 0 and 1, from the original position [42]. In (8), the original positions are at  $f_{CH} \pm f_{spur,N}$ , and FSK modulation will spread the tones to  $f_{CH} + f_{spur,N} \pm (N+1) \cdot 250kHz$  and  $f_{CH} - f_{spur,N} \pm (N-1) \cdot 250kHz$  with 6.02dB degraded amplitudes. This phenomenon is shown on the right side of Figure 3.3 for N=1 and 3. This only applies to FSKs that the product of data duration (1us) and frequency deviation (250kHz)

is 0.5. For even N's, both terms of (8) result in continuous phase modulation that are not a discontinuous phase modulation and the power of the spurs are attenuated greater than 15dB.

A special case occurs when  $|f_{spur,1}| < 250kHz$ , where  $a_N$ ,  $b_N$  changes for data 1 and 0, resulting in a spread spectrum even for odd value of N's, showing attenuation greater than 15dB according to experimental results. Therefore, to focus on the worst-case spurious tones at the output spectrum, we consider the cases when  $|f_{spur,1}| \ge 250kHz$ . In summary, the group of offset positions and amplitudes of the modulated signal's spurious tones resulting from odd harmonics of a PNN can be expressed as follows.

$$f_{ble,spur,N} = \begin{cases} \begin{pmatrix} f_{spur,N} + (1+N)\Delta f \\ f_{spur,N} - (1+N)\Delta f \\ -f_{spur,N} \end{pmatrix}, N = 1 \\ \begin{pmatrix} f_{spur,N} + (1+N)\Delta f \\ f_{spur,N} - (1+N)\Delta f \\ -f_{spur,N} + (1-N)\Delta f \\ -f_{spur,N} - (1-N)\Delta f \end{pmatrix}, N = 3, 5.. \end{cases}$$

$$(9)$$

$$S_{ble,spur,N} = \begin{cases} \begin{pmatrix} S_{pll}(f_{spur,N})/4 \\ S_{pll}(f_{spur,N})/4 \end{pmatrix}, N = 3, 5..$$

(10)

where  $f_{ble,spur,N}$  is a group of frequency offsets from the center frequency  $f_{CH}$  due to spurious tone at  $f_{spur,N}$ ,  $S_{ble,spur,N}$  is a group of amplitudes of spurious tones at each frequency offset and  $\Delta f = 250 \mathrm{kHz}$ .

## 3.2.3 Experimental Results