# **Energy-Efficient Wireless Connectivity and Wireless Charging for Internet-of-Things (IoT) Applications**

by

Omar A. B. Abdelatty

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2021

**Doctoral Committee:**

Professor Amir Mortazawi, Co-Chair Professor David Wentzloff, Co-Chair Professor Michael Flynn Professor Karl Grosh Omar A. B. Abdelatty

omaratty@umich.edu

ORCID iD: 0000-0002-0298-7334

© Omar A. B. Abdelatty 2021

# **DEDICATION**

To my beloved family, friends, and advisors.

#### ACKNOWLEDGEMENT

First and foremost, I would like to thank god for giving me the opportunity to endure this long PhD journey. Second, I would like to express my sincere gratitude to my main advisor, Prof. David Wentzloff and Co-advisor, Prof. Amir Mortazawi for their endless support in every aspect, continuous encouragement, and kind patience. My research contributions would not have been possible without their great mentorship, innovative and deep insightful ideas. They are amazing mentors and an exceptional researchers and I was very lucky to be one of their students. I learned a lot from them both on the personal and professional levels. Special thanks for Prof. Wentzloff for the annual group retreats for the group and the weekly lunches which really strengthen the bonds between the group members. Honestly, I could not ask for a better advisor. I am also deeply grateful for my thesis committee and providing their valuable discussions and feedback to improve the quality of the thesis.

During my PhD journey, I had the opportunity to work in two big labs here at UofM: the Radlab during the first half of my PhD and the Integrated Circuits and VLSI lab throughout the second half of my PhD. I cannot express how much diverse and cumulative experience I learned from the members of both labs. So, initially I would like to extend my gratitude to the whole group members of the WICS lab, previous and present members, who provided endless support during my PhD journey. In particular, I am thankful for my friends: Abdullah Alghaihab, Jaeho Im, Xing Chen, Yao Shi, Hyeongseok Kim, Milad Moossavifar, Kyumin Kwon, Yashwanth Cherivirala, Trevor Odelberg, Aman Gupta, Noah Michels, and Li-Yu Chen with whom I had the great opportunity to work closely and collaborate during my PhD. I want to thank all my friends, previous and current members of MICL, with whom I shared the working space, classroom sessions social events and beneficial technical discussions especially at late and long tapeout nights. You will always find someone there in the office supports you.

I would also like to extend my gratitude to the whole RadLab family; starting with Dr. Adib Nashashibi who has been always a great technical support for all the lab experiments. Also, I would like to thank Prof. Kamal Sarabandi, Prof. Ehsan Afshrai, Prof. Anthony Grbic for all the courses I have taken with and their kindness towards me. I would like to extend my gratitude to all current and former Radlab students, I learned a lot from every one of you. Special thanks to my group mates: Xiaoyu Wang, Milad Koohi, Seungku Lee, Fatemah Akbar, Suhyun Nam, Ruiying Chai and Samar Abdelnasser. Also, the entire Radlab students especially, Amr Ibrahim (my role model), Mostafa Zaky (my closest friend), Zainalabden Khalifa, Faris Alsolamy, Abdelahmed Nasr, Navid Barrani, Behzad Yektakhah, Menglou Rao, Maryam Salim, Abdulrahman Alaqeel, Mohammad Amjadi, Mani Kashanianfard, and so many others friends.

I cannot express how grateful I am for my immediate family in Egypt (Dad: Abdelatty, Mom: Somia, Sisters: Habiba and Huda, Brother: Osama, Brother in-low: Mohamed, and Nieces and Nephews: Reem, Sarah, Yassin) for their extreme emotional support and encouragement. I owe everything I do in my life to my parents; literally, anything I have at the moment is the fruit of their hard work and love for me. I am very blessed to have you on my side always and I cannot describe how grateful I am for all the love you have given me. Finally, my warmest thanks to the Egyptian and Arab community here at UofM who made me feel like home throughout all the social gatherings and fun outings throughout the years. I am grateful for all the moments and memories I have shared with everyone, especially, Dr. Mostafa zaky, Dr. Amr Alaa, Dr. Essam Othman, Dr. Ashraf Shabaan, Dr. Omar Ashraf, Abdelhameed, Hiba Chahat, Fatmah Gharbiah, Sanaa Elsayed , Dr. Osama Gomaa, Dr. Ahmed Mostafa, Ahmed Elhossieny, Dr. Mohamed NoorEldin, Ahmed Elshaarany, Dr. Ahmed Usama, Ali Dowair, Amr Raof, Nasser Eldaghri, Mohammad Vahid Jammali, Hammad Eloutabi and all my other friends if I mistakenly dropped their names in the list.

# TABLE OF CONTENTS

| DEDICATION                                                         | ii         |

|--------------------------------------------------------------------|------------|

| ACKNOWLEDGEMENT                                                    | iii        |

| LIST OF TABLES                                                     | ix         |

| LIST OF FIGURES                                                    | X          |

| ABSTRACT                                                           | xiv        |

| Chapter 1 Introduction and Motivation                              | 1          |

| 1.1. Evolution of Internet-of-Things (IoT) Devices                 | 1          |

| 1.2. IoT Emerging Applications and Requirements                    | 4          |

| 1.3. Wireless Connectivity Landscape for IoT Devices               | 5          |

| 1.4. Bluetooth Low-Energy Standard Overview                        | 7          |

| 1.5. Battery-Powered IoT Devices Limitations                       |            |

| 1.6. Wireless Charging for IoT Devices                             |            |

| 1.7. Dissertation Contributions and Organization                   |            |

| Chapter 2 Bluetooth Communication Leveraging Ultra-Low Power Radio | ) Design18 |

| 2.1 Introduction                                                   |            |

| 2.2 Back-Channel Communication for Energy-Efficient Operation      | 19         |

| 2.2.1 Synchronization Schemes                                      | 19         |

| 2.2.2 Back-Channel Communication Concept                           |            |

| 2.2.3 ULP Back-Channel BLE RX Prototype                            |            |

| 2.3 BLE Radio Design Trends and Considerations                     |            |

| 2.3.1 Receiver Design Trends                                       |            |

| 2.3.2 Transmitter Design Trends                                    |            |

| 2.4 Conclusions and Future Work                                    |            |

| Chapter 3 A 300µW Bluetooth-Low-Energy Backchannel Receiver Employing a<br>Discrete-Time Differentiator-Based Coherent GFSK Demodulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 40                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 40                                                                                      |

| 3.2 RF Front End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 41                                                                                      |

| 3.2.1 Passive I/Q Generation Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 41                                                                                      |

| 3.2.2 LC-DCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 43                                                                                      |

| 3.2.3 Baseband PGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 45                                                                                      |

| 3.3 Proposed GFSK Demodulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 45                                                                                      |

| 3.4 Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 51                                                                                      |

| 3.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 52                                                                                      |

| Chapter 4 A Low Power Bluetooth Low-Energy Transmitter with a 10.5nJ Startup<br>Energy Crystal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                           |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 53                                                                                      |

| 4.2 Transmitter Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 54                                                                                      |

| 4.3 On-Chip Fast-Startup Crystal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 58                                                                                      |

| 4.4 Measurement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 61                                                                                      |

| 4.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 65                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           |

| Chapter 5 A Cell-Based Bluetooth Low-Energy Transmitter Employing RO-Based<br>ADPLL in FinFET12nm Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 66                                                                                      |

| ADPLL in FinFET12nm Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>. 66</b><br>. 66                                                                       |

| ADPLL in FinFET12nm Technology           5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>. 66</b><br>. 66<br>. 69                                                               |

| ADPLL in FinFET12nm Technology         5.1 Introduction         5.2 BLE Transmitter Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>. 66</b><br>. 66<br>. 69<br>. 71                                                       |

| ADPLL in FinFET12nm Technology<br>5.1 Introduction<br>5.2 BLE Transmitter Architecture<br>5.3 Switched-Capacitor Power Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 66<br>. 66<br>. 69<br>. 71<br>. 77                                                      |

| ADPLL in FinFET12nm Technology<br>5.1 Introduction<br>5.2 BLE Transmitter Architecture<br>5.3 Switched-Capacitor Power Amplifier<br>5.4 RO-Based ADPLL                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 66<br>. 66<br>. 69<br>. 71<br>. 77<br>. 81                                              |

| ADPLL in FinFET12nm Technology<br>5.1 Introduction<br>5.2 BLE Transmitter Architecture<br>5.3 Switched-Capacitor Power Amplifier<br>5.4 RO-Based ADPLL<br>5.5 Top Digital Controller                                                                                                                                                                                                                                                                                                                                                                                                                                | . 66<br>. 69<br>. 71<br>. 77<br>. 81<br>. 84                                              |

| <ul> <li>ADPLL in FinFET12nm Technology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 66<br>. 66<br>. 69<br>. 71<br>. 77<br>. 81<br>. 84<br>. 88                              |

| ADPLL in FinFET12nm Technology         5.1 Introduction         5.2 BLE Transmitter Architecture         5.3 Switched-Capacitor Power Amplifier         5.4 RO-Based ADPLL         5.5 Top Digital Controller         5.6 Preliminarily Measurement Results         5.7 Conclusion         Chapter 6 Position-Insensitive Wireless Power Transfer Based on Nonlinear                                                                                                                                                                                                                                                | . 66<br>. 66<br>. 69<br>. 71<br>. 77<br>. 81<br>. 84<br>. 88                              |

| <ul> <li>ADPLL in FinFET12nm Technology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 66<br>. 69<br>. 71<br>. 77<br>. 81<br>. 84<br>. 88<br>. 89                              |

| <ul> <li>ADPLL in FinFET12nm Technology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 66<br>. 69<br>. 71<br>. 77<br>. 81<br>. 84<br>. 88<br>. 89<br>. 89<br>. 94<br>PT        |

| <ul> <li>ADPLL in FinFET12nm Technology</li> <li>5.1 Introduction</li> <li>5.2 BLE Transmitter Architecture</li> <li>5.3 Switched-Capacitor Power Amplifier</li> <li>5.4 RO-Based ADPLL</li> <li>5.5 Top Digital Controller</li> <li>5.6 Preliminarily Measurement Results</li> <li>5.7 Conclusion</li> </ul> Chapter 6 Position-Insensitive Wireless Power Transfer Based on Nonlinear Resonant Circuits <ul> <li>6.1 Introduction</li> <li>6.2 Theory and properties of electrical nonlinear resonant circuits</li> <li>6.3 principle of operation, analysis, and design of nonlinear resonant-based W</li> </ul> | . 66<br>. 69<br>. 71<br>. 77<br>. 81<br>. 84<br>. 88<br>. 89<br>. 89<br>. 94<br>PT<br>104 |

| 6.3.3 Synthesizing the C-V Relationship for the Secondary Nonlinear   |     |

|-----------------------------------------------------------------------|-----|

| Capacitor                                                             | 110 |

| 6.4 Nonlinear WPT Circuit Implementation and experimental results     | 113 |

| 6.5 Conclusion                                                        | 120 |

| Chapter 7 Conclusion and Future Work                                  | 122 |

| 7.1. Summary and Conclusions                                          | 122 |

| 7.2. Future Work                                                      | 124 |

| Appendix 1 Bluetooth Low Energy Standard Requirments for Transmitters | 126 |

| Appendix 2 List of Acronyms                                           | 129 |

| BIBLIOGRAPHY                                                          | 133 |

## LIST OF TABLES

| Table 2.1 Comparison table for the state-of-the-art Bluetooth-Low Energy receivers.       33 |

|----------------------------------------------------------------------------------------------|

| Table 2.2 Comparison table for the state-of-the-art Bluetooth-Low Energy transmitters        |

| Table 3.1 Comparison with recent fully-compliant and backchannel BLE receivers               |

| Table 4.1 Measured XO Performance Summary and Comparison to The State-Of-Art                 |

| Table 4.2 Measured BLE TX Performance Summary and Comparison to The State-Of-Art 64          |

| Table 5.1 Summary of the Fully-Synthesizable ADPLL Specifications.       80                  |

| Table 6.1 Component Specifications for The Implemented WPT Circuit                           |

| Table 8.1 BLE Standard Transmission Power Classes.    126                                    |

| Table 8.2 BLE Standard Transmit Spectrum Mask.    127                                        |

| Table 8.3 BLE Standard Maximum Allowable Frequency Drifts in a Packet                        |

| Table 8.4 PLL Specifications Based on the BLE Standard Requirements                          |

# **LIST OF FIGURES**

| Figure 1.1 The roadmap of the Internet of Things from 2000 onwards                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Predictions for overall connected devices by 2025: (a) Source: CABA [18], (b) Source: Statista                                                                                                                                                                                                                                                                                                                                       |

| Figure 1.3 IoT connectivity landscape                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 1.4 (a) Wide range of consumer IoT applications, (b) self-powered wireless sensor systems used for health monitoring purposes                                                                                                                                                                                                                                                                                                            |

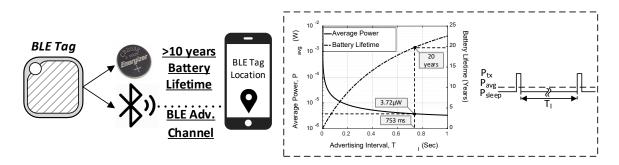

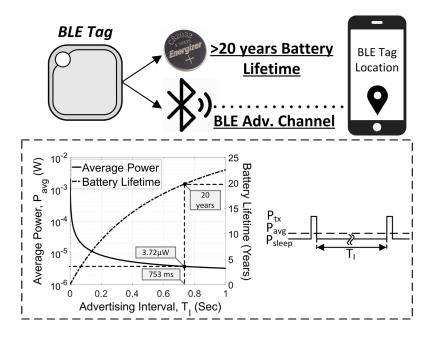

| Figure 1.5 A typical IoT BLE application (left), the tradeoff between the required average power consumption and battery lifetime in duty-cycled transmission targeting a specific latency (right)                                                                                                                                                                                                                                              |

| Figure 1.6 (a) near-field versus (b) far-field wireless charging technologies 12                                                                                                                                                                                                                                                                                                                                                                |

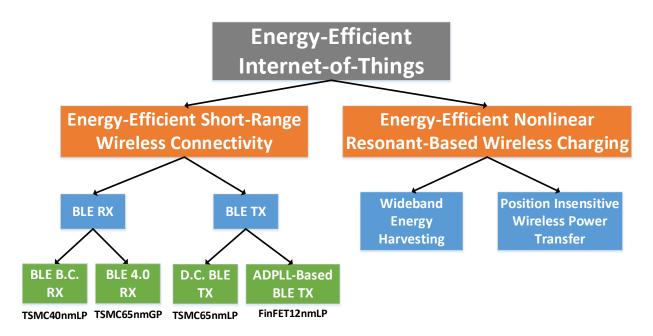

| Figure 1.7 Overview of the Dissertation TopicsError! Bookmark not defined.                                                                                                                                                                                                                                                                                                                                                                      |

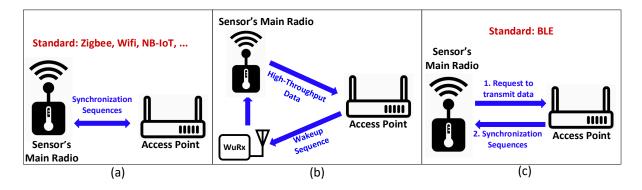

| Figure 2.1 Different synchronization schemes resulting in different complexity and power budget requirements: (a) synchronous; (b) wake-up receivers; (c) asynchronous                                                                                                                                                                                                                                                                          |

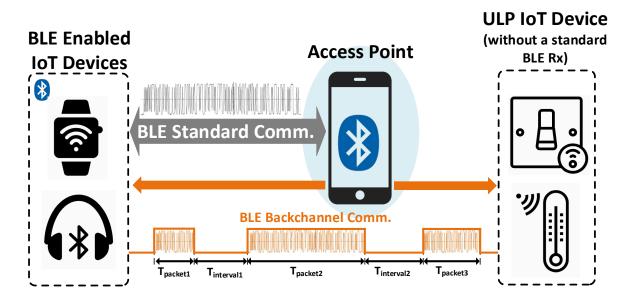

| Figure 2.2 Concept of BLE (Bluetooth Low-Energy)-based back-channel communication 24                                                                                                                                                                                                                                                                                                                                                            |

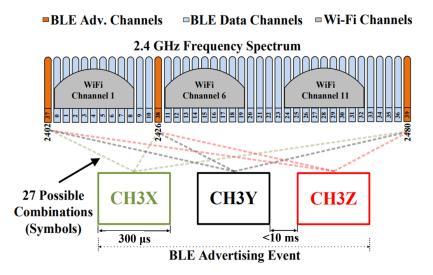

| Figure 2.3 Structure of a BLE advertising event                                                                                                                                                                                                                                                                                                                                                                                                 |

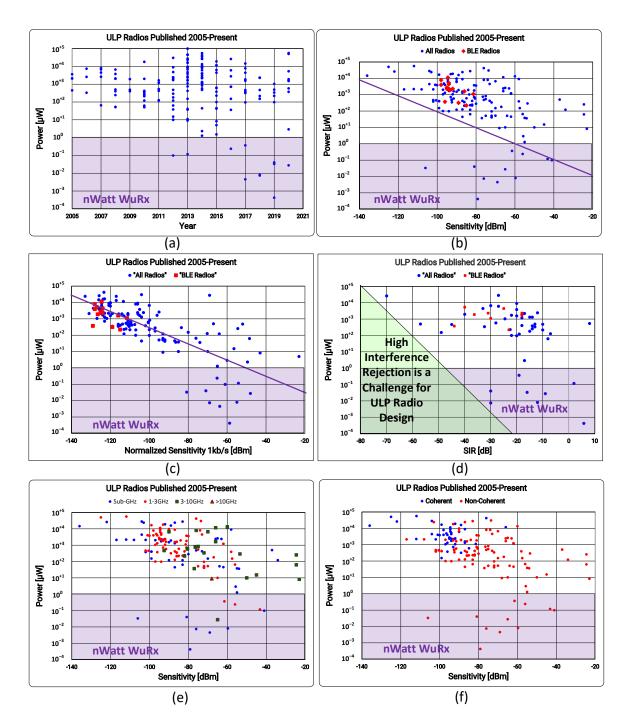

| <ul> <li>Figure 2.4 ULP (ultra-low power) receivers' survey showing different design trade-offs. (a) Power trend of published receivers over years; (b) power consumption versus sensitivity; (c) power consumption versus normalized sensitivity; (d) power versus signal-to-interference ratio (SIR); (e) power versus sensitivity at different frequency ranges; and (f) power versus sensitivity for different modulation schemes</li></ul> |

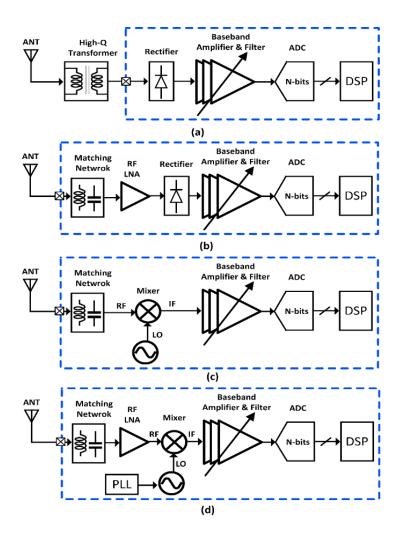

| Figure 2.5 Common architectures of low power receivers: (a) energy-detector first; (b) energy-detector + LNA first; (c) mixer-first without PLL; (d) LNA-first architectures                                                                                                                                                                                                                                                                    |

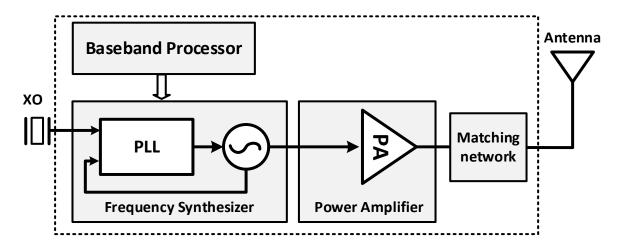

| Figure 2.6 Conventional architecture of BLE transmitters                                                                                                                                                                                                                                                                                                                                                                                        |

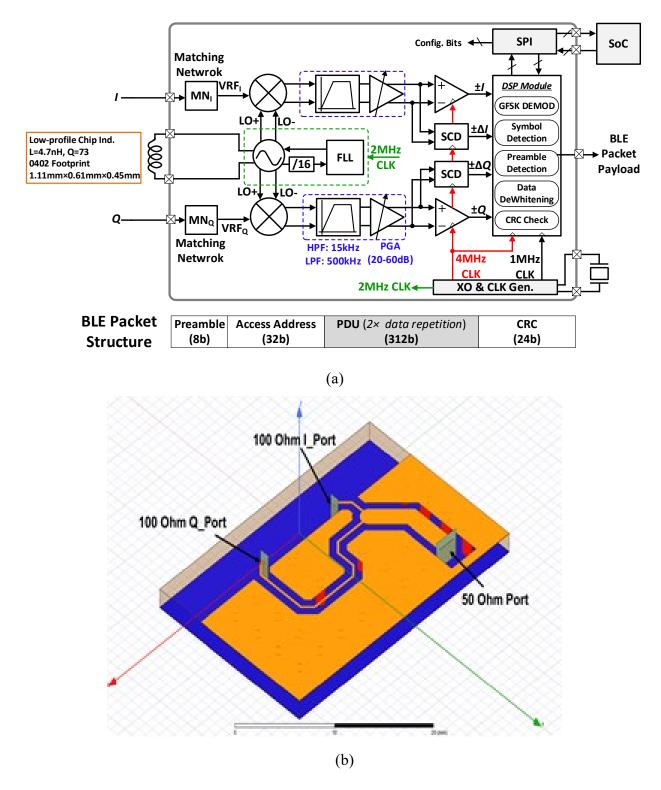

| Figure 3.1 Architecture of the proposed backchannel RX with a passive I/Q generation which can be achieved using b) a $50\Omega$ single port antenna employing a lossless T-junction power divider                                                                                                                                                                                                                                              |

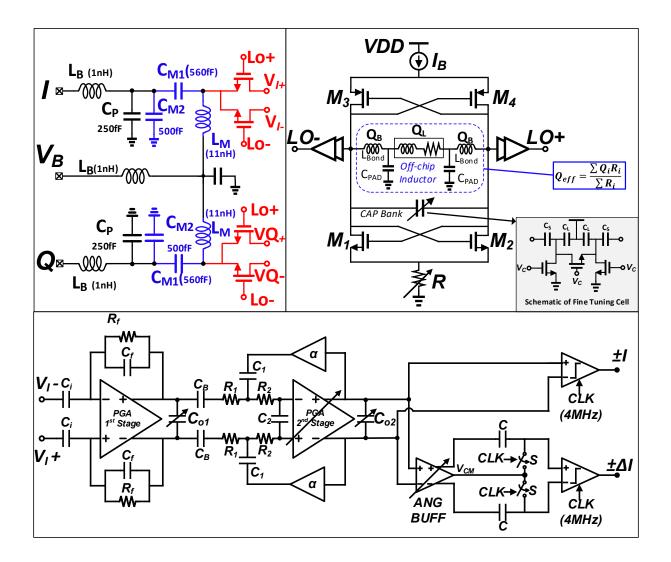

| Figure 3.2                                                         | RF front-end and analog baseband circuitry showing: input matching network, mixer biasing, LC-DCO, two-stage PGAs and SCD of the I-channel                                                                                                                                                                               |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

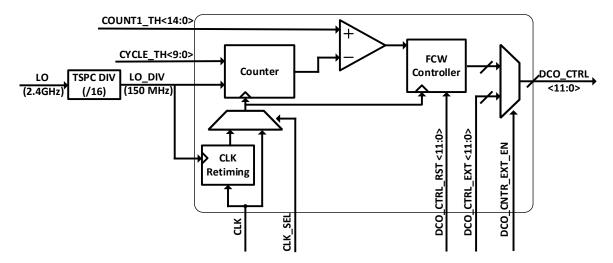

| Figure 3.3                                                         | Block diagram of the counter-based FLL                                                                                                                                                                                                                                                                                   |

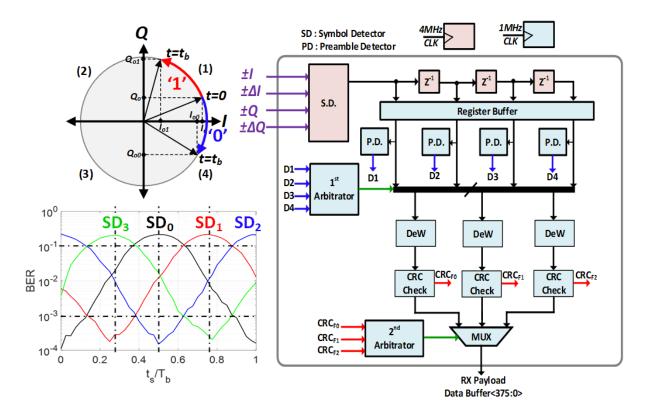

| Figure 3.4                                                         | Proposed GFSK demodulation, symbol detection, packet synchronization, and CRC check                                                                                                                                                                                                                                      |

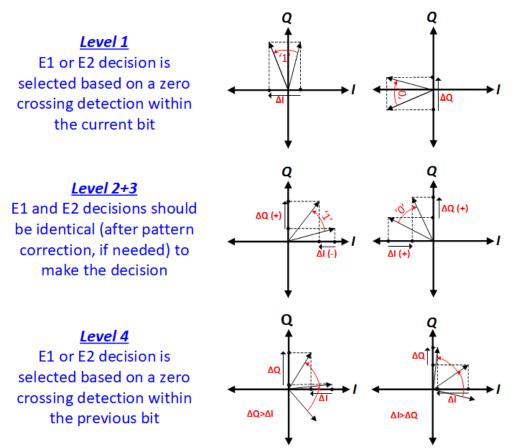

| Figure 3.5                                                         | 5 Proposed 4-level symbol detection algorithm implemented in DBB. The SD is<br>independent on the random input phase of the received signal                                                                                                                                                                              |

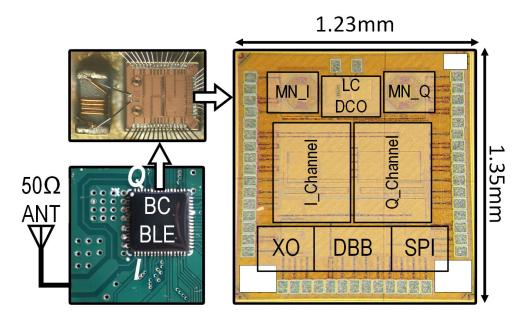

| Figure 3.6                                                         | On-board I/Q generation, in-package inductor, and Die micrograph 50                                                                                                                                                                                                                                                      |

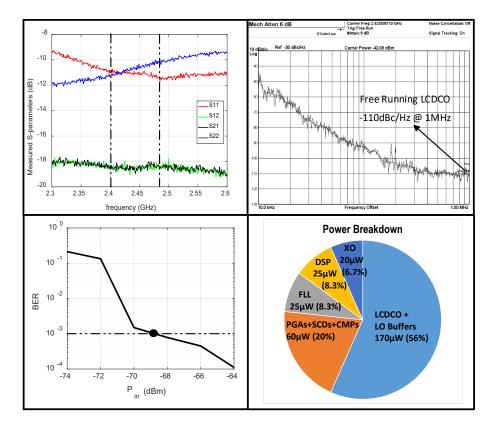

| Figure 3.7                                                         | Measured performance of BLE receiver (S-parameters, LCDCO phase noise, sensitivity) and the power breakdown of the receiver                                                                                                                                                                                              |

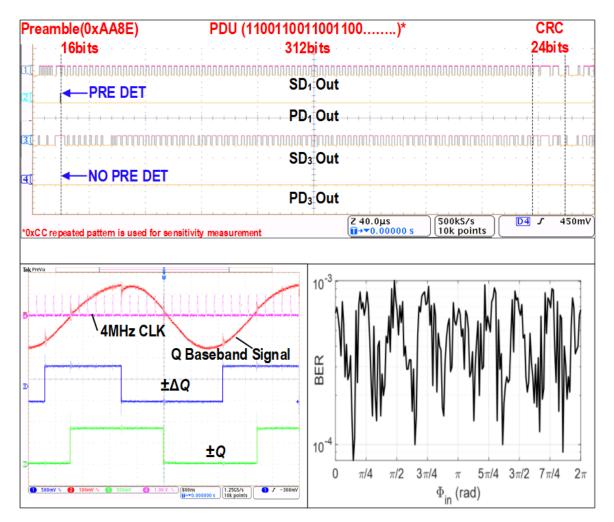

| Figure 3.8                                                         | Timing diagram of: 1) a received packet, 2) baseband signal. The simulated effect of the random input phase on the BER showing the robustness of the proposed symbol detection algorithm                                                                                                                                 |

| Figure 4.1                                                         | System level application for the proposed low power BLE TX 54                                                                                                                                                                                                                                                            |

| Figure 4.2                                                         | Simplified block diagram showing the architecture of the proposed low power complete BLE TX                                                                                                                                                                                                                              |

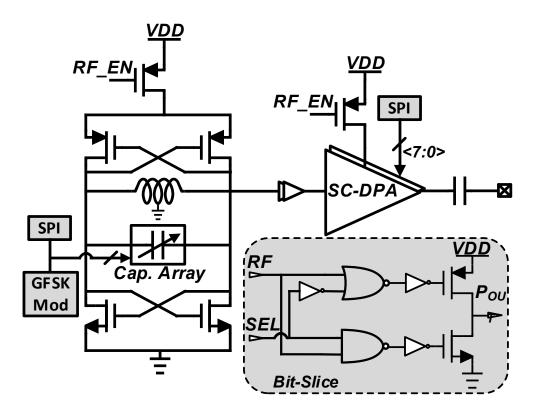

| Figure 4.3                                                         | Circuit schematic of RF front-end                                                                                                                                                                                                                                                                                        |

| E                                                                  |                                                                                                                                                                                                                                                                                                                          |

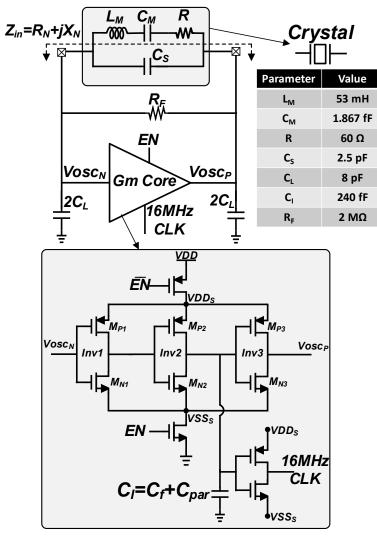

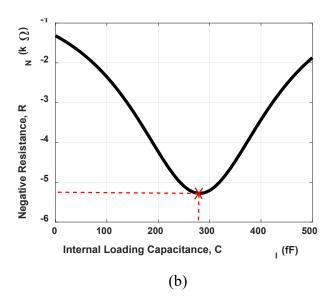

| Figure 4.4                                                         | (a) Circuit schematic of the fast-startup low-power crystal oscillator using three-stage capacitively loaded inverters and the crystal's equivalent circuit, and (b) simulation results of the series equivalent negative resistance versus the internal loading capacitance showing the optimum value of C <sub>I</sub> |

|                                                                    | capacitively loaded inverters and the crystal's equivalent circuit, and (b) simulation results of the series equivalent negative resistance versus the internal loading                                                                                                                                                  |

| Figure 4.5                                                         | capacitively loaded inverters and the crystal's equivalent circuit, and (b) simulation results of the series equivalent negative resistance versus the internal loading capacitance showing the optimum value of C <sub>I</sub>                                                                                          |

| Figure 4.5<br>Figure 4.6                                           | capacitively loaded inverters and the crystal's equivalent circuit, and (b) simulation<br>results of the series equivalent negative resistance versus the internal loading<br>capacitance showing the optimum value of C <sub>I</sub>                                                                                    |

| Figure 4.5<br>Figure 4.6<br>Figure 4.7                             | capacitively loaded inverters and the crystal's equivalent circuit, and (b) simulation<br>results of the series equivalent negative resistance versus the internal loading<br>capacitance showing the optimum value of C <sub>I</sub>                                                                                    |

| Figure 4.5<br>Figure 4.6<br>Figure 4.7<br>Figure 4.8               | capacitively loaded inverters and the crystal's equivalent circuit, and (b) simulation<br>results of the series equivalent negative resistance versus the internal loading<br>capacitance showing the optimum value of C <sub>I</sub>                                                                                    |

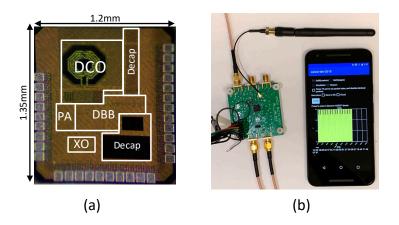

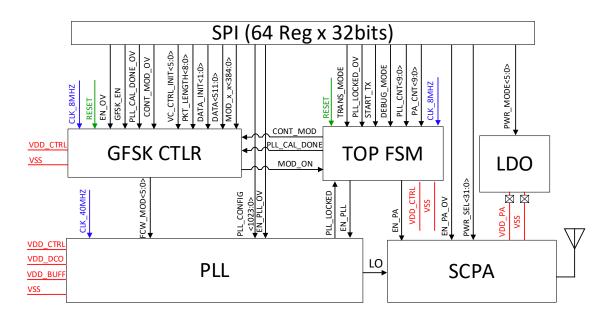

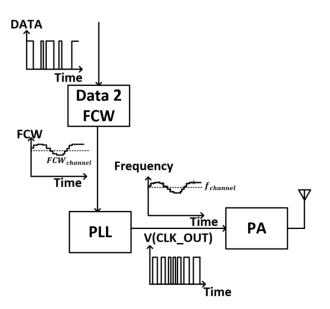

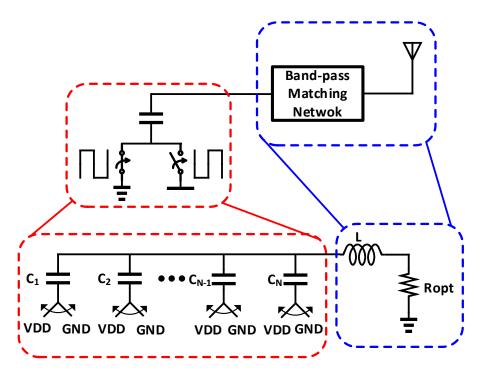

| Figure 4.5<br>Figure 4.6<br>Figure 4.7<br>Figure 4.8<br>Figure 5.1 | capacitively loaded inverters and the crystal's equivalent circuit, and (b) simulation<br>results of the series equivalent negative resistance versus the internal loading<br>capacitance showing the optimum value of C <sub>1</sub>                                                                                    |

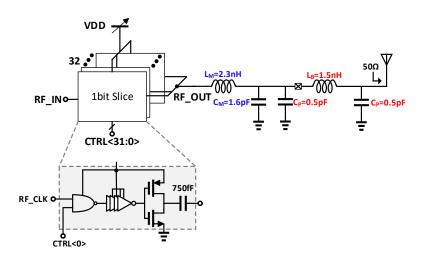

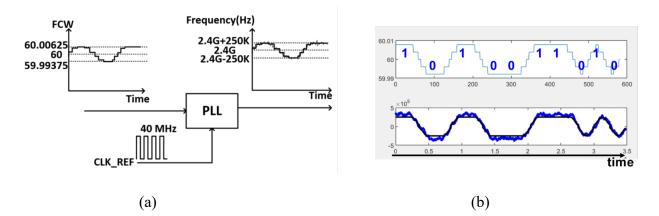

| Figure 5.4 Complete (a) schematic and (b) layout of the SCPA                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

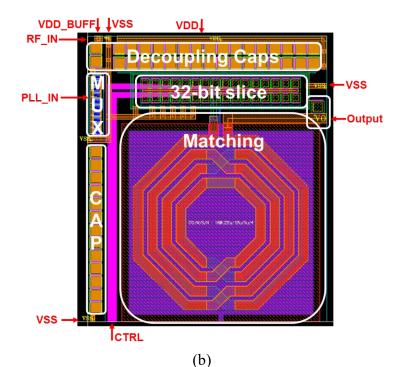

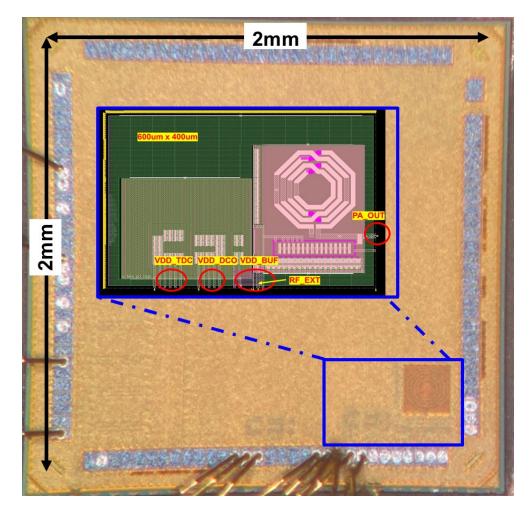

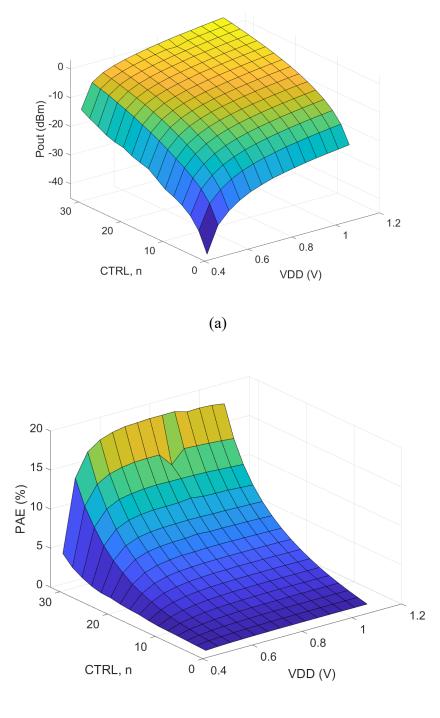

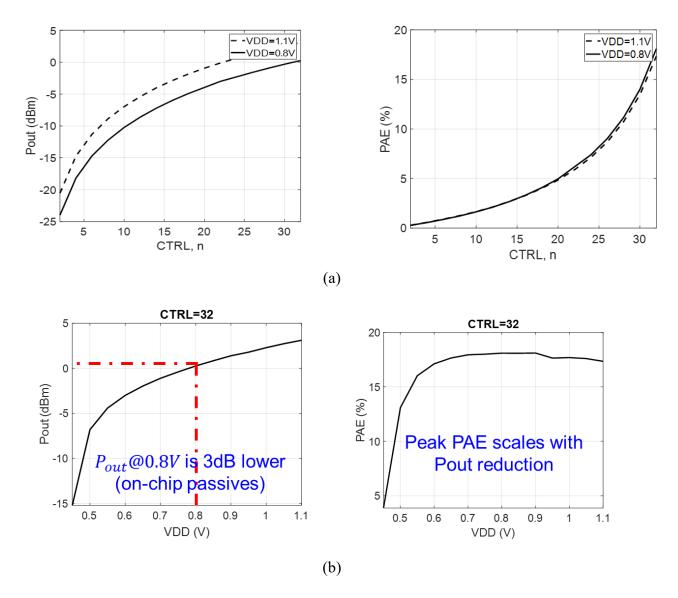

| Figure 5.5 Pout and PAE of the SCPA while tuning (a) digital control word and (b) supply voltage.                                                                                                                       |

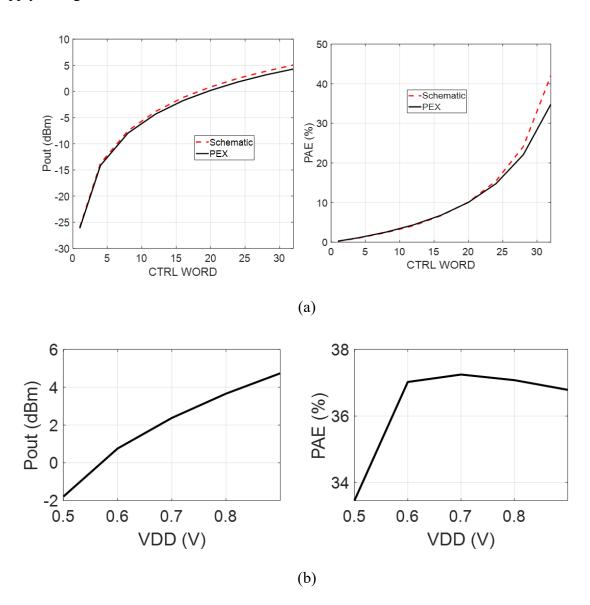

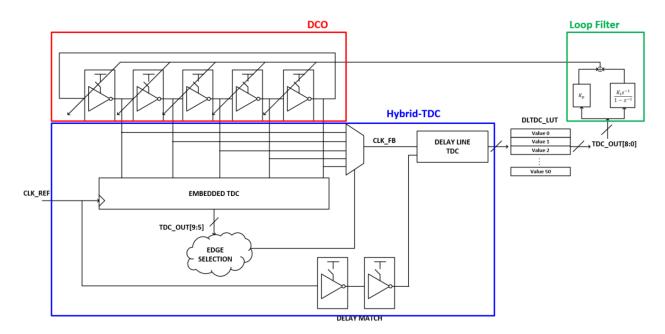

| Figure 5.6 (a) PLL functional block diagram and (b) Matlab behavioral simulation results 77                                                                                                                             |

| Figure 5.7 Schematic of the proposed ADPLL                                                                                                                                                                              |

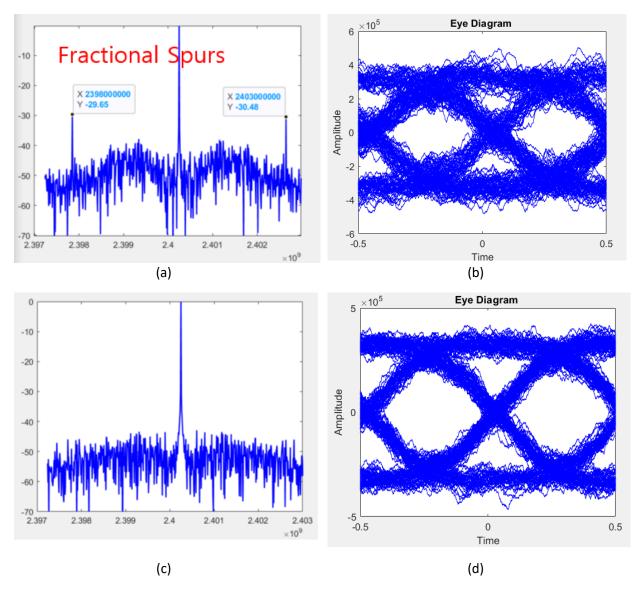

| Figure 5.8 Matlab behavioral simulation results. (a) and (b) are the results with only embedded TDC. (c) and (d) are the results with the hybrid-TDC                                                                    |

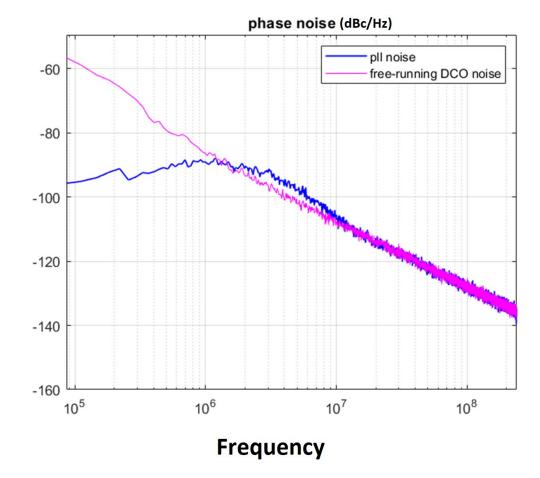

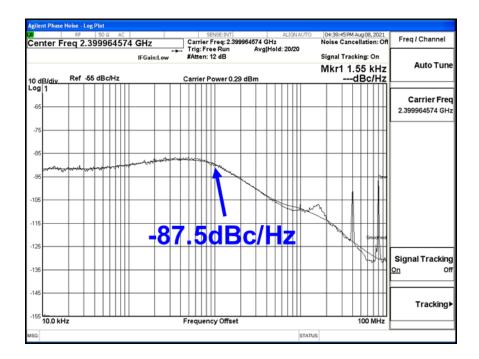

| Figure 5.9 Phase noise plot of PLL with FCW = 60.025                                                                                                                                                                    |

| Figure 5.10 Implemented FSM for the top level controller                                                                                                                                                                |

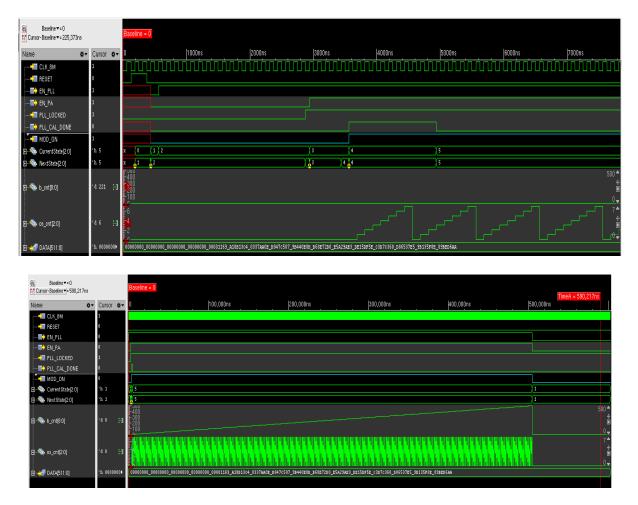

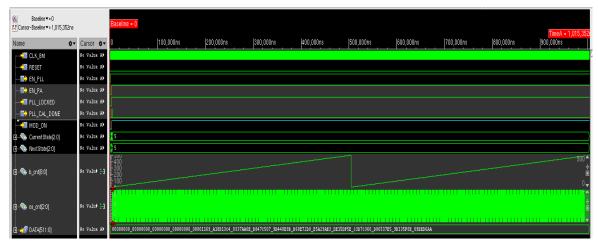

| Figure 5.11 FSM timing diagram for single transmission mode                                                                                                                                                             |

| Figure 5.12 FSM timing diagram for continous transmission mode                                                                                                                                                          |

| Figure 5.13 FSM timing diagram for debugging mode                                                                                                                                                                       |

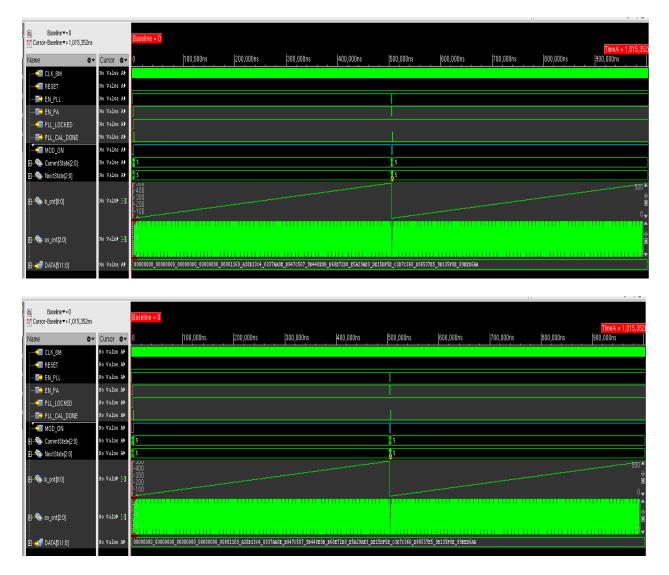

| Figure 5.14 Die micrograph of the entire SoC chip                                                                                                                                                                       |

| Figure 5.15 Measured (a) Pout and (b) PAE of the SCPA versus CTRL and VDD tuning schemes.                                                                                                                               |

| Figure 5.16 Measured Pout and PAE of the SCPA at (a) nominal supply voltage when sweeping the CTRL word, (b) the maximum CTRL word when sweeping the supply voltage                                                     |

| Figure 5.17 Measured phase noise of integer-N PLL                                                                                                                                                                       |

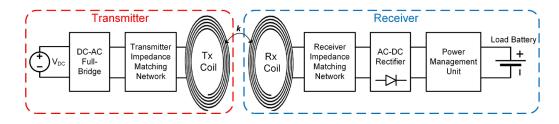

| Figure 6.1 Typical block diagram of an inductively coupled WPT system                                                                                                                                                   |

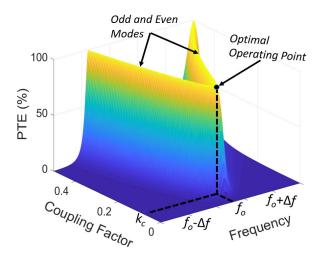

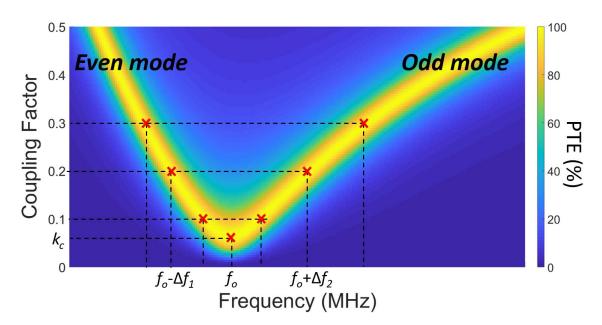

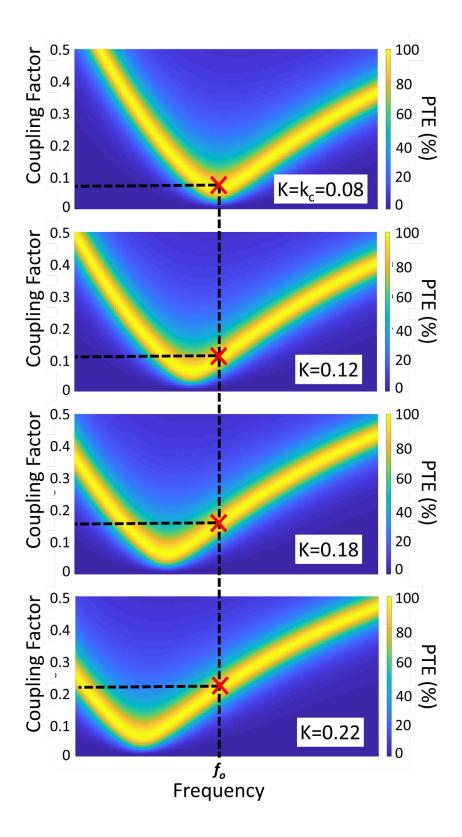

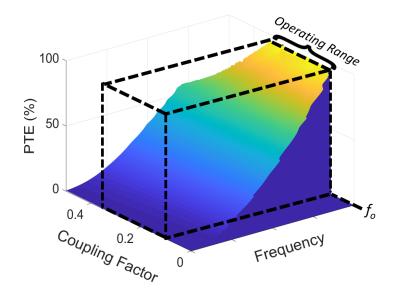

| Figure 6.2 PTE vs. operating frequency and coupling factor presenting the frequency splitting phenomenon for the conventional linear WPT systems                                                                        |

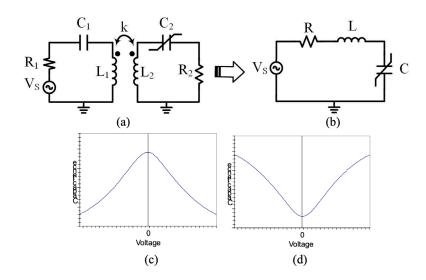

| Figure 6.3 (a) Nonlinear resonant-based inductively coupled WPT circuit, (b) equivalent single nonlinear series resonance circuit, (c) symmetrical bell-shaped C-V curve, and (d) symmetrical well-shaped C-V curve     |

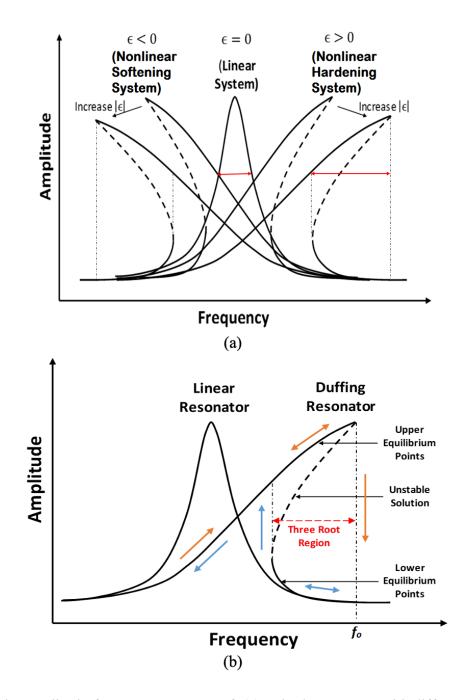

| Figure 6.4 The amplitude-frequency response of: (a) a single resonator with different nonlinearity coefficient ( $\epsilon$ ), (b) Duffing resonator (red and blue arrows show the hysteresis loop and jump phenomenon) |

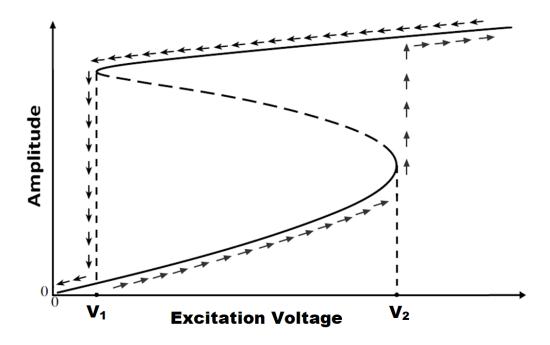

| Figure 6.5 The resonance amplitude versus excitation amplitude response                                                                                                                                                 |

| Figure 6.6 PTE vs. frequency and coupling factor (k), showing the optimum operating frequency at different coupling factors                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.7 Multiple plots of the PTE vs. frequency and coupling factor (k), associated with the adjusted resonance frequencies at different coupling factors                                                                                                                 |

| Figure 6.8 PTE vs. operating frequency and coupling factor for the presented nonlinear resonant-<br>based WPT circuits                                                                                                                                                       |

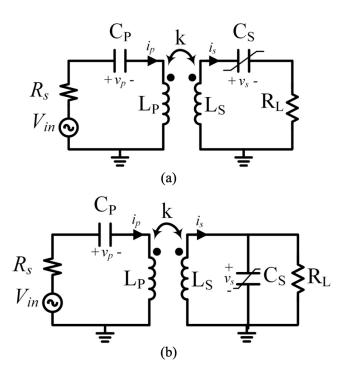

| Figure 6.9 Circuit schematics of the nonlinear resonant-based WPT (a) Series-Series topology, and (b) Series-Parallel topology                                                                                                                                               |

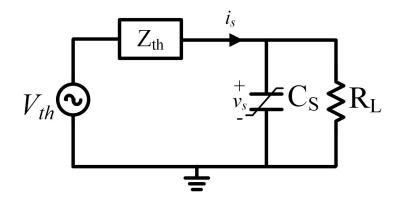

| Figure 6.10 The equivalent single nonlinear resonator at the receiver side of the series-parallel topology                                                                                                                                                                   |

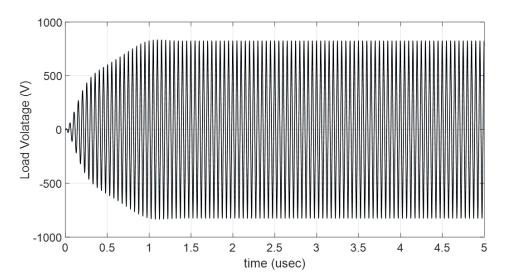

| Figure 6.11 Simulated transient response of the voltage across a 5kΩ load resistance in the<br>proposed nonlinear resonant-based WPT circuit at k=0.22. (The source available power<br>is 60 W)                                                                              |

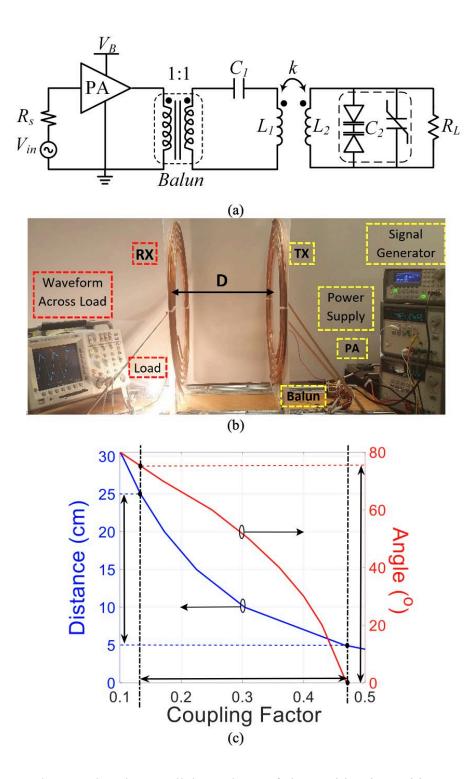

| Figure 6.12 Implemented series-parallel topology of the position-insensitive WPT circuit: (a) circuit schematic, (b) experiment setup, and (c) measured coupling factor between the transmit and receive coils versus the transmission distance and the angular misalignment |

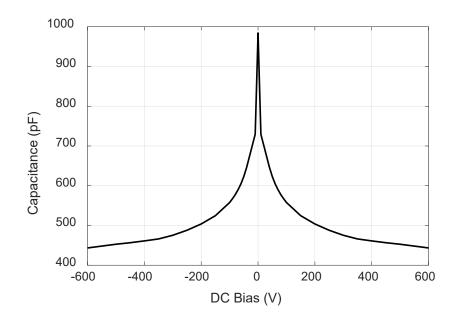

| Figure 6.13 Measured C-V response of the optimized combination of the nonlinear capacitors.                                                                                                                                                                                  |

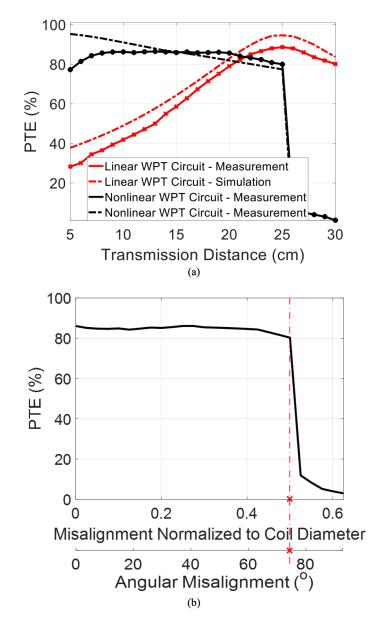

| Figure 6.14 Measured PTE versus (a) distance variation, and (b) lateral misalignment offset and angular misalignment between the transmit and receive coils                                                                                                                  |

| Figure 8.1 BLE Standard GFSK parameters definition                                                                                                                                                                                                                           |

#### ABSTRACT

During the recent years, the Internet-of-Things (IoT) has been rapidly evolving. It is indeed the future of communication that has transformed Things of the real world into smarter devices. To date, the world has deployed billions of "smart" connected things. Predictions say there will be 10's of billions of connected devices by 2025 and in our lifetime we will experience life with a trillion-node network. However, battery lifespan exhibits a critical barrier to scaling IoT devices. Replacing batteries on a trillion-sensor scale is a logistically prohibitive feat. Self-powered IoT devices seems to be the right direction to stand up to that challenge. The main objective of this thesis is to develop solutions to achieve energy-efficient wireless-connectivity and wirelesscharging for IoT applications.

In the first part of the thesis, I introduce ultra-low power radios that are compatible with the Bluetooth Low-Energy (BLE) standard. BLE is considered as the preeminent protocol for short-range communications that support transmission ranges up to 10's of meters. Number of low power BLE transmitter (TX) and receiver (RX) architectures have been designed, fabricated and tested in different planar CMOS and FinFET technologies. The low power operation is achieved by combining low power techniques in both the network and physical layers, namely: backchannel communication, duty-cycling, open-loop transmission/reception, PLL-less architectures, and mixer-first architectures. Further novel techniques have been proposed to further reduce the power the consumption of the radio design, including: a fast startup time and low startup energy crystal oscillators, an antenna-chip co-design approach for quadrature generation in the RF path, an ultralow power discrete-time differentiator-based Gaussian Frequency Shift Keying (GFSK) demodulation scheme, an oversampling GFSK modulation/demodulation scheme for open loop transmission/reception and packet synchronization, and a cell-based design approach that allows automation in the design of BLE digital architectures. The implemented BLE TXs transmit fullycompliant BLE advertising packet that can be received by commercial smartphone.

In the second part of the thesis, I introduce passive nonlinear resonant circuits to achieve wide-band RF energy harvesting and robust wireless power transfer circuits. Nonlinear resonant circuits modeled by the Duffing nonlinear differential equation exhibit interesting hysteresis characteristics in their frequency and amplitude responses that are exploited in designing self-adaptive wireless charging systems. In the magnetic-resonance wireless power transfer scenario, coupled nonlinear resonators are proposed to maintain the power transfer level and efficiency over a range of coupling factors without active feedback control circuitry. Coupling factor depends on the transmission distance, lateral, and angular misalignments between the charging pad and the device. Therefore, nonlinear resonance extends the efficient charging zones of a wireless charger without the requirement for a precise alignment.

## **Chapter 1**

## **Introduction and Motivation**

#### 1.1. Evolution of Internet-of-Things (IoT) devices

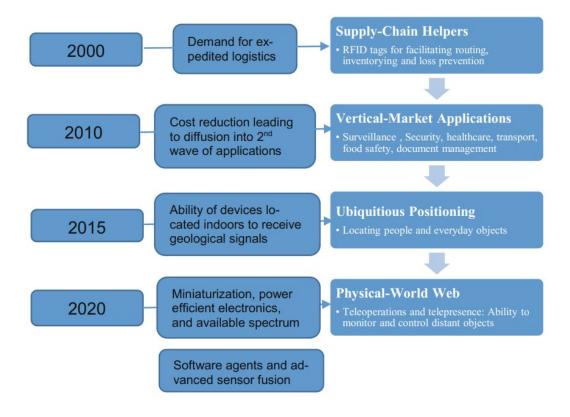

The first idea of the Internet of Things (IoT) appeared almost three decades ago, but core technologies behind it, e.g. Internet, RFID, and embedded computer systems, had already existed and have been under development for many years prior that [1]. Sensor nodes were developed in the mid-1990s to sense the data from uniquely identified embedded devices and seamlessly exchange the information to realize the basic idea of IoT [2-4]. In 1999, device-to-device communication was introduced by Bill Joy in his taxonomy of the internet, and the term 'Internet of Things' was used for the first time by Ashton [5, 6]. From 2000 and onwards, IoT connectivity gained momentum for many applications, becoming part of a shared vision for the future of the internet. The roadmap of the Internet of Things from 2000 onwards is shown in Fig. 1.1 [1].

The considerable rise in the number of objects connected to the internet, either by wire or wireless, has caused research growth in this area from both industry and academia [2]. Today, the growth of small and cheap computing devices endowed with sensing and communication capabilities promote the realization of the vision of IoT. Virtually all everyday objects can be connected to the internet, including smart homes, medical equipment, sports equipment, and vehicles. Therefore, IoT is a concept that has the potential to impact our lives and the way we work [7]. It can dramatically improve security, energy efficiency, education, health, and many other

aspects of daily life for consumers [8-13]. IoT is an evolution of mobile, embedded applications and everything that is connected to the internet to integrate greater communication ability and use data analytics to extract meaningful information. Thus, two main components of an "IoT object" are required: (1) the ability to capture data via sensors and (2) transmit data via the Internet [14, 15].

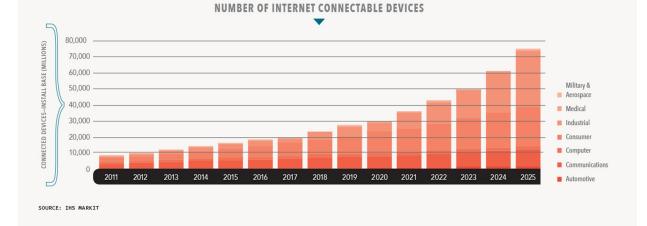

Experts predict that the IoT will have a substantial economic impact with that many possible applications and probably more unimagined ones. As per McKinsey, the growth of the IoT market would be from 4 trillion USD to 11 trillion USD by 2025 [16], whereas Statista predicts it to be 1.6 trillion USD by 2025 [17]. Regarding number of connected IoT devices worldwide, CABA anticipates >70 billion devices on the Internet by 2025 [18] (Fig. 1.2(a)) while Statista forecasts >30 billion connected devices by 2025 [19] as shown in Fig. 1.2(b).

Figure 1.1 The roadmap of the Internet of Things from 2000 onwards [1].

# **OVERALL DEVELOPMENT OF IOT DEVICES**

The Continental Automated Buildings Association (CABA) has found that by the end of 2025, there will be approximately 70 billion IoT-connected devices.

(a)

(b)

Figure 1.2 Predictions for overall connected devices by 2025: (a) Source: CABA [18], (b) Source: Statista [19].

#### **1.2.** IoT emerging applications and requirements

Given the recent advances in ubiquitous computing, there are currently many diverse IoT applications for many different environments expected to enhance and improve the quality of everyday life for the end-user community. Major application domains include but are not limited to smart homes, smart cities, intelligent transportation systems, industrial and smart health care [20]. Those various applications have different characteristics and requirements in terms of latency and data rate. It can also be broadly divided into two main categories: consumer IoT (cIoT) and industrial IoT (iIoT) [21]. Consumer IoT aims at improving quality of life of consumers by saving time and money. It also involves the interconnection of consumer electronic devices along with other technology belonging to user environments such as homes, offices, and cities. Conversely, industrial IoT focuses on the integration between Operational Technology (OT) and Information Technology (IT) [22] and on how smart machines, networked sensors, and data analytics can improve business-to-business services. It generally implies machine-to-machine interactions, either for application monitoring (e.g., process monitoring in chemical production plants, vehicle fleet tracking, among others), or as part of a self-organized system, with a distributed control which does not require human intervention (i.e., autonomic industrial plants) [23].

The two service domains share some general communication requirements, such as scalability, the need for lean protocol stack implementations in constrained devices, and friendliness to the IP ecosystem. Nonetheless, the specific communication requirements of iIoT and cIoT can be very different in terms of reliability, QoS (latency, throughput, etc.), and privacy. In cIoT, communications are typically machine-to-user and usually in the form of client-server interactions. Desirable features of IoT are low power consumption, ease of installation, integration, and maintenance. For instance, the advent of fitness and health tracking systems, smartwatches,

and sensor-rich smartphones require a high power efficiency to enable long-term monitoring by small, portable devices as part of a "smart" environment or integrated into our daily wearings [24].

Energy efficiency is perhaps the most crucial aspect of IoT, in particular, because most IoT devices are battery-powered and are expected to be operational for a very long period without human intervention. The time interval between changing batteries for such a smart connected device is a significant cost factor to be considered. Previous research has shown that most energy expended in IoT devices is due to communication [25]. Therefore, energy efficiency has to be considered in the design of both hardware and software. There are several medium access control (MAC) protocols that support duty cycling, allowing the radio to be put to sleep (i.e., low power mode) for periods when it is not expecting to receive data, therefore extending battery life. Energy management techniques also play an essential role in low power operation through lightweight protocols and scheduling optimization, for instance [26] and energy harvesting, where IoT devices can harvest ambient energy from various sources. Moreover, this would also allow the connectivity of new smart device applications that are not currently deployed. A minimum of a ten-year battery life span of operation will be achieved for the daily connectivity of these devices.

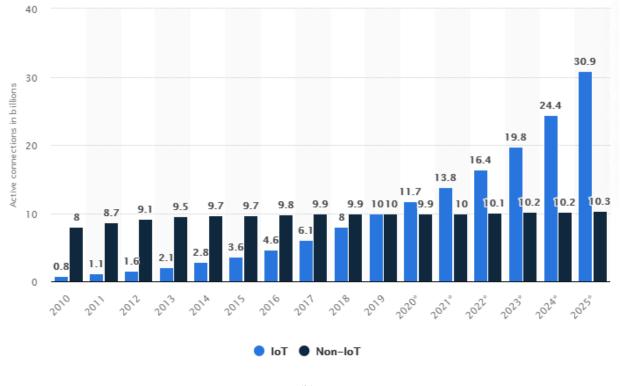

#### 1.3. Wireless connectivity landscape for IoT devices

The IoT landscape includes the diverse availability of connectivity solutions as shown in Fig. 1.3. Although there is still no unified solution for IoT at this point, several different communication technologies have been proposed and are currently in operation, having been deployed in a number of devices worldwide. Both long-range and short-range communication standards will be utilized for most connections to achieve both Massive IoT and Critical IoT connectivity through either traditional cellular IoT or Low Power Wide Area Networks (LPWAN).

Common communication technologies use for different application domains include:

- Personal Area Networks  $\rightarrow$  Bluetooth Low Energy

- Home Automation Systems  $\rightarrow$  ZigBee

- iIoT LoRa, WirelessHART

- Broader coverage → Low Power Wi-Fi, Low Power Wide Area Networks (LPWA), Cellular communications (such as 3GPP - 4G machine-type communications, MTC).

LPWA technologies are designed for IoT applications because of their unique features like wide-area coverage, high energy efficiency, channel bandwidth, data rate, and low power consumption [20]. This technology represents the various technologies currently being used in connecting both sensors and controllers to the internet without the intervention of existing traditional Wi-Fi or cellular networks. Among these promising technologies are SigFox, Ingenu RPMA, and LoRa. Current future demand for internet connectivity of "Things" has motivated the cellular technology to introduce their own IoT devices connectivity landscape solutions such as LTE Cat-M1 (also known as eMTC), EC-GSM-IoT, and NB-IoT (also called LTE Cat-NB1) that will enhance and enable future IoT use cases. LPWA networks are currently being deployed for IoT applications, including smart cities, building management systems, asset monitoring, smart agriculture, etc.

Legacy short-range wireless network technologies are currently being used to support short-range M2M communication applications, including Bluetooth, ZigBee, and low-power Wi-Fi. These technologies are a viable and best fit for consumer use cases of the IoT. Still, they may not support civic, industrial, and other related IoT applications for which the demands are beyond the capacity of their characteristic features.

Figure 1.3 IoT connectivity landscape.

#### 1.4. Bluetooth Low Energy (BLE) Standard Overview

Bluetooth was designed based on the IEEE's 802.15.1 wireless personal area communication standard [27] to be used for short-range (up to 50m) ad-hoc communication between devices with achievable data rates in the low Mbps. Bluetooth Low Energy (BLE) was introduced to improve energy consumption suitable for low-power, control, and monitoring applications (e.g., automotive, entertainment, home automation, etc.). BLE operates in the 2.4 GHz ISM band and defines 40 channels with 2MHz channel spacing. The modulation scheme used is Gaussian Frequency Shift Key (GFSK) modulation. To the final aim of achieving low power usage, BLE uses (and thus, scans) only three advertising channels, which are used for device discovery, connection set up, and broadcast transmission. The other 37 data channels are dedicated to the bidirectional exchange of short bursts of data between connected devices. BLE also sets up connections very quickly, which further minimizes the radios on-time. BLE uses an adaptive frequency hopping algorithm on top of the data channels where the signal switches carriers over a predetermined pattern of channels to make it more robust to interference and multi-path fading [28].

However, one of the drawbacks is the restriction of only one-to-one communication between only two devices at a time. BLE currently only supports a single-hop topology, namely piconet, with one master device communicating with several slave nodes and a broadcast group topology, with an advertiser node broadcasting to several scanners. The Bluetooth Special Interest Group proposed the Bluetooth Smart Mesh working group to define and standardize a new architecture for mesh networking for BLE. This will enable extended communication range and simplify deployments of BLE networks for IoT. BLE is envisaged as a connectivity solution for short-range communication in IoT applications, including smart energy, healthcare, and smart home applications [29].

#### 1.5. Battery-powered IoT devices limitations

The power consumption of IoT devices is widely recognized as the limiting factor to scaling the number of battery-powered IoT devices [30]. Assuming a scenario where a billion devices are deployed with an expected battery life of one year, this would result in replacing 2.7 million batteries each day. In reality, this unacceptable number imposes significant logistical burdens in operational deployments and reduces the utility of IoT devices in different sectors. In addition, batteries represent a logistically prohibitive maintenance problem that requires a large maintenance workforce, presenting a daunting challenge for individual facilities where maintenance resources are already at capacity. Therefore, the battery needs to last as long as the product's life, which can be on the order of 10 years for an embedded device performing signal processing and wireless communication [31].

Unfortunately, current battery lifetimes of BLE sensors are typically <1 year, far short of the 10-year target for other IoT protocols such as cellular narrowband IoT (NB-IoT) and LoRa

devices. However, reducing the power consumption and the operating supply voltages enable the design of self-powered IoT devices in which energy harvesting technologies can be used to power the node from the environment [32]. One growing application in this field is body-powered wearable devices in mobile health technologies that allow remote and continuous health monitoring, as shown in Fig. 1.4 (b) [33]. Another application in the industrial sector is in machine health monitoring (MHM), where self-powered ULP sensors can be deployed to observe specific abnormal patterns in the monitored physical/mechanical signals of a machine for early failure detection. Low-power operation facilitates harvesting of the machine's vibrational energy using piezoelectric materials to charge super-capacitors used to power the sensor [34].

Figure 1.4 (a) Wide range of consumer IoT applications, (b) self-powered wireless sensor systems used for health monitoring purposes.

Typically, the RF radio accounts for a significant portion of the aggregate power profile of the device. Thus, each data transmission operation performed by a battery-powered node shortens its subsequent lifetime, limiting the amount of data transmittable before needing to recharge/replace the battery. In a typical IoT application, it is reasonable to assume the radio consumes 60–90% of the operating power budget [35]. The active power for a single BLE packet

transmission is usually several mWs, in addition to the startup energy of the frequency synthesizer and the crystal oscillator [35]. To extend the battery's lifetime, aggressive duty-cycling can be implemented [31]. This technique leads to a significant increase in the operational lifetime for battery-powered devices. Using the advertising interval (TI) defined as the time between two successive transmission events, the intended battery lifetime can be estimated (preferably >10 years). A good example application is a tracking device that establishes a Bluetooth connection to a smartphone. Using a common CR2031 coin battery with an energy density of 653 mWh, the required average power consumption for a 20-year lifetime is  $3.7 \mu$ W. The TI can be calculated as shown in Fig. 1.5. For a more accurate estimation, several additional factors need to be considered, including: (1) the battery self-discharge rate (usually <20 years), (2) the battery capacity degradation by temperature variations, and (3) the startup/shutdown overhead energy which might add extra ~50% to the power budget. All the aforementioned factors will limit the device from achieving the desired lifetime values.

Figure 1.5 A typical IoT BLE application (left), the tradeoff between the required average power consumption and battery lifetime in duty-cycled transmission targeting a specific latency (right).

#### 1.6. Wireless charging for IoT devices

As a fast developing technique, wireless power transmission (WPT) incredibly performs cordless energy migration [37, 38]. This seemingly incredible way can change our traditional

energy utilization patterns in different applications, such as low-power wide-area networks, portable electronic devices, implanted medical devices, integrated circuits, solar-powered satellites, electric vehicles (EVs), unmanned aerial vehicles (UAVs), etc. Through its remarkable characteristics of flexibility, position-free, and mobility, the WPT technique has been taken as an ideal technical solution in the near future, especially for smart home applications, to energize electrical-driven devices within certain specific regions. According to a study by ABI research, despite the economic restraints of COVID-19, the consumer spending on home automation is expected to reach \$317 billion by 2026 [39]. ABI research also found that the next generation of smart home customers is looking for low-cost and flexible devices that are easy to set up. Therefore, manufacturers that plan to grow their market share in this emerging space should make their devices convenient to use, with wireless charging for smart homes.

Mostly, IoT devices are powered by batteries. Two basic battery-powered device issues limit their popularization: short battery life and high initial cost. A major limitation of devices powered by battery is finite battery capacity dominated by the power consumption of radios. As IoT devices communicate with each other, a large amount of energy is consumed due to which devices operate for a limited duration only as long as the battery lasts [40]. To prolong the battery life of an IoT device, potential tradeoffs would be low data rate and high latency which lower power by essentially leaving the radio off for more of the time. Furthermore, when the device battery is exhausted, the network may be interrupted. Thus, the lifespan of an IoT device is crucial to the success of an application.

One of the solutions to this problem is to use replaceable batteries. This solution of replacing the battery may be effective for small IoT systems. Still, for large IoT systems, this solution is not practical because the cost of maintaining and replacing billions of batteries is very

high. Therefore, effective charging strategies are needed. Different core wireless charging technologies have been developed and classified into: inductive coupling, magnetic resonant coupling, and energy harvesting of electromagnetic (EM) radiation [41] as shown in Fig. 1.6. Wireless power transfer via an electromagnetic (EM) wave has gained attention thanks to its capability of far-field power transmission [42]. Inductive coupling provides highly efficient charging for a single target at a very close range. It is often applied when charging mobile phones, electric toothbrushes, and other devices.

On the other hand, magnetic resonant coupling provides high-efficiency charging for devices at a distance, making it suitable for wireless sensing networks, mobile devices, and electric vehicles. However, it is susceptible to coupling factor variation. Unlike magnetic wireless power transfer techniques such as inductive coupling and magnetic resonant coupling, the radio frequency (RF) energy harvesting technique uses a radiative EM wave to convey power through free space. Therefore, the RF energy transfer enjoys a relatively longer energy transfer distance compared to magnetic wireless power transfer [43]. However, the wireless power transfer via an EM wave suffers from low end-to-end transfer efficiency because of severe power attenuation. But it can still be used in wireless sensing networks owing to the small size of the receiving power device.

- Near-Field:

- Simple, convenient way to recharge consumer devices on the go

- Require precise positioning

- Far-Field:

- Provides ubiquitous wireless power

Challenges: low sensitivity and efficiency

- Gnanenges, iow sensitivity and emiciency

https://www.eeworldonline.com/far-field-wireless-charging-will-be-a-game-changerfor-consumer-industrial-and-medical-products/

Figure 1.6 (a) near-field versus (b) far-field wireless charging technologies.

Therefore, to achieve energy-efficient operation in wireless sensor networks and maintain network communication, efforts in reducing the energy consumption of the IoT device shall be combined with the efforts to improve the range and efficiency of wireless charging.

#### **1.7. Dissertation Contribution and Organization**

The main objective of this thesis is to develop a complete solution to achieve energyefficient networks for IoT applications. The thesis is divided into two main parts: 1) design of low power BLE radios for energy-efficient wireless connectivity solutions, and 2) design of robust and high efficiency wireless power transfer and wide-bandwidth energy harvesting circuits for energyefficient wireless charging solutions. The main contributions of this thesis can be summarized as:

- A novel coherent-based ultra-low power GFSK demodulation architecture is designed and tested for BLE receivers that allows eliminating power-hungry PLLs and utilizing open-loop reception schemes. The demodulator deals independently with the I and Q waveforms in time-domain for proper symbol detection.

- Antenna-chip co-design approach is introduced for quadrature generation in the RF path with only 3dB NF penalty using lossless power dividers; significantly reducing the power consumption of BLE receivers.

- 3. A BLE TX with few µWs average power consumption is achieved through duty cycling thanks to the fast-startup time and low startup energy on-chip crystal oscillator; achieving vigilant health wearables with self-powered operation.

- 4. A cell-based design approach for a digital BLE TX architecture is presented and implemented for the first time in FinFET technology; leveraging the automatic placeand-route capabilities of the FASoC framework.

5. Self-adaptive nonlinear resonant circuits represented by Duffing equations have been proposed to achieve robust wireless power transfer and wideband energy-harvesting circuits with zero overhead power consumption and control/feedback circuitry. This technique is generic and can be applied for wide range of power levels and frequencies. An overview of the topics discussed in this thesis is portrayed in Fig.1.7. To accomplish the stated goal, different system architectures and circuit techniques have been proposed, designed, fabricated and measured to prove the concept as summarized in Fig 1.7.

Figure 1.7 Overview of the Dissertation Topics

The rest of the thesis is organized as follows:

Chapter 2 discusses the different strategies that have been proposed to tackle the limited capacity of battery-powered IoT devices both in physical and network layers. The ultimate goal is to lower the power consumption of radios without sacrificing other important metrics like latency, transmission range and robust operation under the presence of interference. Joint efforts in

designing energy-efficient wireless protocols and low-power radio architectures result in achieving sub-100  $\mu$ W operation. One technique to lower power is back-channel (BC) communication which allows ultra-low power receivers to communicate efficiently with commonly used wireless standards like BLE while utilizing the al-ready-deployed infrastructure. In this chapter, a review of BLE back-channel communication and its forms is introduced. Additionally, a comprehensive survey of ULP radio design trends and techniques in both Bluetooth transmitters and receivers is presented [44].

Chapter 3 presents a 300 $\mu$ W backchannel receiver (RX) compatible with the Bluetooth-Low-Energy (BLE) standard for ultra-low power Internet-of-Things (IoT) applications. A PLLless, mixer-first zero-IF architecture is proposed to achieve the low power operation featuring an antenna-chip co-design for lossless quadrature (I/Q) generation in the RF path. A novel 10 $\mu$ W switched-capacitor differentiator-based GFSK demodulator is presented. The demodulator exhibits a robust operation under I/Q phase and amplitude imbalances and operates at a 1MHz baseband clock frequency. The proposed backchannel communication within the packet's payload is achieved through 2× data repetition. The chip is designed and fabricated in CMOS 40nm technology. The RX achieves -69dBm sensitivity for 0.1% bit error rate (BER) at 0.5Mbps effective data rate [45].

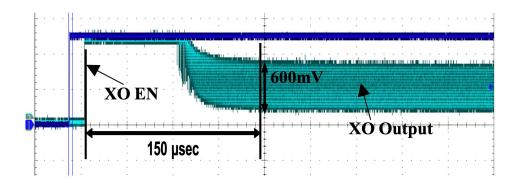

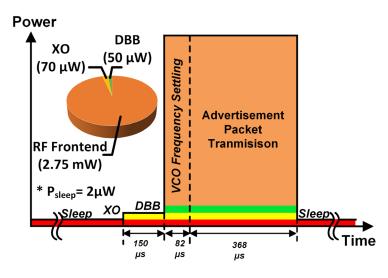

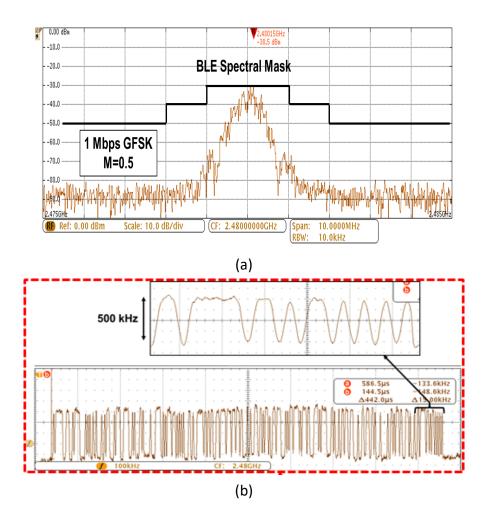

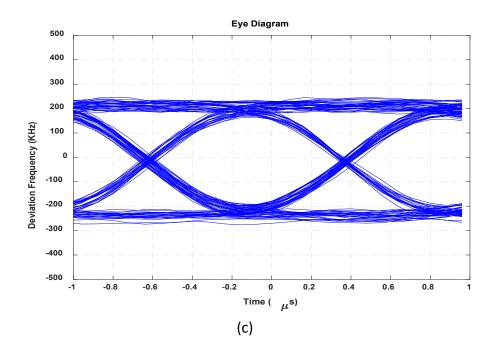

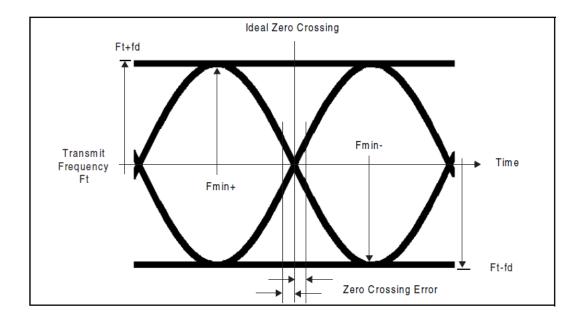

Chapter 4 present fully-integrated Bluetooth Low-Energy (BLE) transmitter (TX) for Internet-of-Things (IoT) applications. The BLE TX achieves a total energy per bit of 3.5nJ in an open-loop transmission scheme due to the ultra-low startup energy of the system. The overall system architecture of the BLE TX includes an RF front-end, a 16 MHz crystal oscillator (XO), a GFSK modulator, and a digital baseband including a SPI interface. An enhanced capacitively loaded three-stage inverter chain XO is proposed, featuring a 10.2nJ startup-energy, a 150µs startup time, and a 70 $\mu$ W steady-state power. The steady-state frequency inaccuracy of the XO is 14 ppm with less than 26ps cycle-to-cycle jitter. The BLE TX is fabricated in 65nm CMOS technology and it consumes an average power of 2.17mW to transmit an advertisement packet consisting of 368 bits entirely over 600 $\mu$ s including the startup time. Duty-cycling operation is implemented through power gating achieving an average power consumption of 3.72 $\mu$ W (1.86× sleep power) when transmitting a BLE advertising message every 753ms. In our target application, by using these techniques, we are able to extend a common coin battery's lifetime to more than 20 years [46].