## Ultra-Low Power Receivers for IoT Applications: A Review

David D. Wentzloff<sup>1</sup>, Abdullah Alghaihab<sup>2</sup>, Jaeho Im<sup>3</sup> University of Michigan, Ann Arbor, MI <sup>1</sup>wentzlof@umich.edu, <sup>2</sup>abdulalg@umich.edu, <sup>3</sup>jaeim@umich.edu

Abstract— Efficient wireless connectivity is an important requirement for IoT applications and has attracted a lot of research interest recently. The receivers designed for such applications need to be low power while still supporting sufficient communication range and co-existing with other receivers that share the same frequency band. In addition, supporting adopted communication standards is key for ubiquitous integration with the existing infrastructure. This paper presents a review of the recent design trends and techniques in ultra-low power receivers for IoT applications.

Index Terms—Low power receivers, Receiver design tradeoffs, RF energy detection, mixer-first wake-up receiver, backchannel receivers.

#### I. INTRODUCTION

With the coming of age of the Internet of Things (IoT), demand on ultra-low power (ULP) receivers will continue to boost tremendously. Innovations in both the system architecture and circuits implementation are essential for the design of truly ubiquitous receivers for IoT applications. RF interference will increase since the limited bandwidth is shared with a rapidly growing number of IoT devices using multiple heterogeneous wireless communication standards. Integrated solutions for interference rejection pose a real challenge in ULP receiver design since they typically require high power and will increase the receiver total power significantly, especially with narrowband channels The design challenge in receivers for IoT applications is to minimize the power consumption with an adequate sensitivity level in a congested frequency spectrum using highly integrated solutions while still being compatible with an adopted communication standard [3, 4].

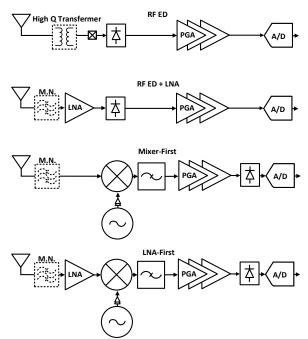

Multiple approaches to reduce the receiver's power consumption have been reported recently [5–10]. These primarily tackle the most power hungry blocks, such as the RF local oscillator (LO) and RF low noise amplifiers (LNAs). For example, RF energy detection is used to convert the incoming RF signal to DC without using any RF local oscillators, which leads to significant power reduction but at the expense of sensitivity. In addition, removing active RF gain will lower the power further [11]. Mixer-first architectures avoid using RF gain but still use an RF LO to down-convert the signal to baseband. This efficiently enhances the receiver's sensitivity and

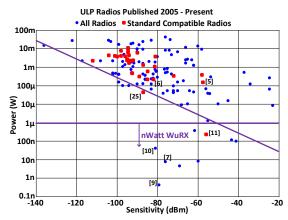

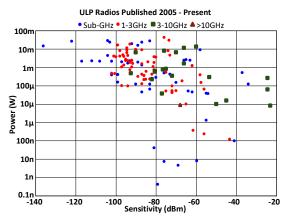

Fig.1. Ultra-low power radio survey: sensitivity vs. power

selectivity compared to RF energy detection since the gain and filtering is done at baseband [5, 6, 12–16].

This paper includes a survey of the recent literature in ULP receiver design. The low power design trends and techniques published recently are discussed in Section II. To address the power and performance tradeoffs in standard compatible receivers, two design approaches are presented in sections III and IV. The first is a BLE compatible backchannel receiver in which the message is embedded in a standard compliant packet and can be received by an ULP receiver. The second is a Wi-Fi wake-up receiver compliant with the wake-up mode defined by the IEEE 802.11ba standard. Finally, conclusions are drawn in Section V.

#### II. ULTRA-LOW POWER RECEIVERS DESIGN TRENDS

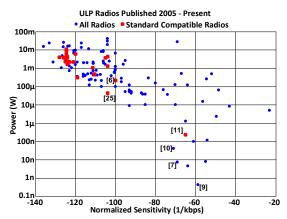

A survey of ULP receivers published in top tier circuits journals and conferences is done to identify the research directions in their design and its limitations [17]. Fig.1 shows the power vs sensitivity (range) trade-off for the recent 179 published ULP receivers. With the exception of nanowatt wake-up receivers, an empirical line with a slope of –1 decade/20dB bounds the performance. This implies the power will increase by a factor of 10x for a 10x increase in the receiver range (assuming a path-loss coefficient of 2). When the sensitivity is normalized to the data rate (Fig.2), however, the power vs sensitivity trade-off becomes more settled since nanowatt receiver have relatively low data rates. In both figures, standard compliant receivers clearly

tend to be higher power. This is expected since most standards nowadays have stringent requirements on sensitivity, interference rejection and frequency accuracy. To achieve these specifications, high power receiver blocks might become required such as LNAs, active filters with sharp frequency response, and phase locked loops (PLLs) with accurate crystal frequency references.

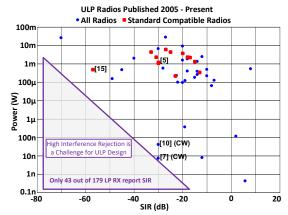

The signal to interference rejection (SIR) performance of ULP receivers is shown in Fig.3. The trade-off can be clearly observed where only a few standard complaint ULP receivers report their selectivity performance, and they consume >100µW. This can be attributed to RF downconversion and active filtering for interference rejection, requiring high power to synthesize a high Q filter response, which is done traditionally by cascading multiple active filter stages. On the other hand, off chip passive filtering is possible but will mean lower system integration and increased cost. For example in [18, 19], off-chip RF MEMS are used to enhance the selectivity performance of the receiver. Network level solutions, such as hopping the frequency to avoid collisions, can boost the effective blocker rejection performance as will be discussed in section III.

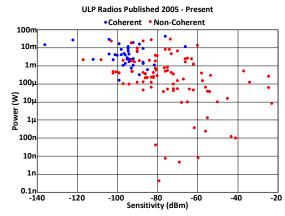

The modulation scheme plays an important role in the specifications of the receiver and hence its power consumption [2]. As seen in Fig.4, coherent communication (e.g. BPSK, OFDM, QAM) requires significantly higher power to demodulate. This is because the carrier phase is needed for coherent detection which necessitates using a PLL in the receiver.

The following design trends are observed in recent publications:

#### A. Nanowatt wake-up receivers:

By utilizing an all passive RF front-end, the RX power can be reduced significantly to the nanowatt level. This is achieved using an RF envelope detector to convert the incoming signal to DC (Fig.5). However, an RF envelope detector has a large bandwidth which limits the sensitivity of such architecture to worse than -60 dBm [11] due to the high noise bandwidth. The sensitivity can be further improved by ~ 20dB by using a high Q transformer at the front-end which provides passive gain and filtering [7, 10] (Fig.5). With this architecture, the integrated interference mitigation techniques used are mostly limited to continuous wave interferes (CW) which can be characterized as an additional DC offset for the comparator [18]. This assumption is not valid for all wireless channels since they experience some level of signal fading which makes these techniques less effective in a real environment. Another limitation of this architecture is it does not support high frequencies due to the large shunt capacitance in RF detectors [20]. Fig.6 shows that all receivers consuming less than 10 µW operate at a frequency lower than 3 GHz. Subthreshold analog and digital logic are common to

Fig.2 Ultra-low power radio survey: normalized sensitivity vs. power.

Fig.3 Ultra-low power radio survey: SIR vs. power.

Fig.4 Ultra-low power radio survey: sensitivity vs. power for coherent and non-coherent modulation.

achieve sub 1-µW power levels [11]. For very low data rates, bit-level duty cycling have been reported [18]. This allows for improved sensitivity levels with low average power at the expense of very low data rate.

Fig.5 Low power radio architectures.

#### B. Mixer-first receivers for selectivity:

Another design trend to save power is to avoid using active RF gain (LNA) while using a mixer as a first stage instead [21–25] (Fig.5). Since the first RX stage dominates its noise performance, mixer-first receivers suffer from higher noise figure (NF), when optimized for low power consumption, which degrades their sensitivity (range). Nevertheless, this architecture can still achieve decent selectivity levels with a sub-mW power budget [26]. In socalled mixer-first receivers, the dominant block in terms of power consumption is the local oscillator and its buffers. In order to reduce the LO power, the conventional LC oscillator can be replaced with a ring oscillator (RO) especially in more advanced CMOS nodes [27]. However, ROs have worse frequency stability making it harder to design the receiver without a significant performance degradation in its sensitivity and/or selectivity [5]. Alternatively, an LC oscillator can have its inductor offchip to overcome the limited quality factor for on-chip inductors resulting in a significant power reduction by up to 75% compared with fully on-chip LC oscillators [13]. Although these off-chip inductors can be found in very small form factors, it is not a fully integrated solution, which might not suit some IoT applications.

### C. LNA-first receivers for long range:

Long range applications require sensitivity levels beyond -100dBm. To achieve this, a LNA-first topology is usually used. Similar to RF ED based wake-up receivers; bit-level duty cycling was applied also in LNA-first receivers [28] to reduce the average power. In addition,

Fig.6 Low power radio survey: sensitivity vs. power for coherent and non-coherent modulation.

lower supply voltages have been used to improve the power efficiency of LNAs [29]. In [30], a low voltage quadrature LNA was adopted in a current-reuse topology resulting in a power consumption of 600µW for the RF front-end, transimpedance amplifier and baseband filter. In addition, [31] presents a direct-conversion BLE receiver using a subthreshold current-reuse LNA.

#### D. Standard compatibility for widespread adoption:

Given the clear power and performance trade-off discussed in this section, one of the challenges in ULP design is to still be able to communicate through an existing adopted standard. The next two sections will present two designs using two approaches to overcome the power and performance trade-off. The first relies on embedding a back-channel message in standard compliant BLE packets [5, 32]. The RX can detect the sequence of BLE advertising channels are used and the timing gaps between them to encode data. The second approach utilizes the wakeup messaging in the IEEE 802.11ba standard to relax the receiver specifications while still being able to receive messages from standard complaint Wi-Fi transmitters [6].

# III. BLE BACK-CHANNEL RECEIVER WITH ENHANCED INTERFERENCE REJECTION

The BLE standard provides a low power solution to connect IoT nodes with mobile devices, however, the power of maintaining a connection with a reasonable latency remains the limiting factor in defining the lifetime of event-driven BLE devices. BLE receiver power consumption is in the milliwatt range [3, 33, 34] and can be duty-cycled for average powers around 30µW, but at the expense of long latency. A recent work presents the concept of BLE back-channel (BC) communication as a wakeup mechanism that bridges the gap between ULP and standard compliant BLE receivers [11]. This provides a low-power receive mode without compromising on latency but it is also susceptible to interference in the crowded 2.4 GHz

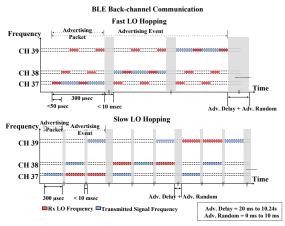

Fig. 7 The concept of back-channel communication in fast and slow modes.

band as it senses the signal without discriminating between sources using different BLE channels.

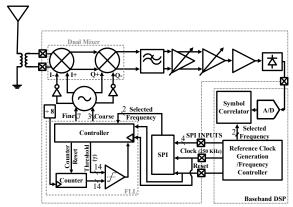

This section presents two prototypes of BLE backchannel receivers that include channel select filters to improve ACI rejection [5]. Both receivers are BLE compatible and can be used with off the shelf BLE transmitters. The first chip is a 150 µW ring oscillator (RO) based receiver with a dual-mixer front-end to save power by using an LO at half the RF frequency. The second chip is a 1.2 mW LC oscillator based receiver with a RF LNA resulting in enhanced frequency stability of the oscillator and improved sensitivity. As a result, the second prototype can support faster frequency hopping. In both designs, channel selectivity is improved by 1) using directconversion with narrow baseband filtering (1 MHz) and by 2) defining each BC message based on the presence of packets in three channels instead of only one, which reduces the impact of blockers. Both BC receiver (BC RX) implementations use FSK communication by detecting the hopping sequence on the three BLE advertising channels, which can be specified in any sequence according to the BLE standard. Consequently, these receivers can wake up from a BLE compatible message sent by a mobile device. Depending on the LO frequency hopping speed, the backchannel communication uses either a fast or slow mode as shown in Fig. 7. In the fast mode, and since the receiver is detecting the energy of advertising channels successively, the LO hopping period between all three channels should be less than  $T_{packet}/2$  to ensure capturing each packet's energy for a certain channel. On the other hand, in the slow mode, the hopping period should be at least  $T_{event}/2$  to ensure capturing a complete advertising event comprising transmissions in all three channels. To achieve the fast hopping, and because the receiver has a narrow bandwidth to help its selectivity performance, the LO frequency has to be stable enough to detect the energy in a short time

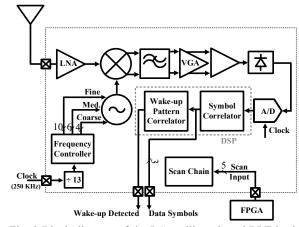

Fig. 8 Block diagram of the RO based BLE back-channel receiver (prototype I).

Fig. 9 Block diagram of the LC oscillator based BLE back-channel receiver (prototype II).

window. In our prototypes, an LC oscillator, which has around 20 dB improvement in phase noise at 1 MHz offset compared with the RO, was used to implement the fast hopping exploiting its superior frequency stability even when running open loop.

In this work, we proposed exploiting frequency diversity gain from the multi-channel advertising events discussed in Section II to improve the blocker rejection performance. Assuming fast LO hopping, and when any single advertising channel is jammed by a nearby strong interferer, the transmitted message can be estimated from the remaining two advertising channels. This is done by setting the required threshold for a valid BC message to be two-thirds of the maximum which allows estimating the received BC message from just two out of three channels. The proposed interference rejection solution is possible since the frequency gaps between the three channels are 24 MHz and 54 MHz, which are relatively large compared with the receiver's bandwidth of only 1 MHz. As a typical strong blocker such as Wi-Fi only affects a single advertising channel, BC modulated messages achieve

Fig. 10 Measured signal-to interference ratio for (a) prototypes I and II vs. interference offset frequency. (b) prototype II vs. BLE channels assuming BC message communication with frequency hopping.

improved BLE/non-BLE blocker rejection performance using only relaxed low-power baseband filters.

Fig. 8 shows the top level block diagram of the ring based BLE back-channel receiver. A mixer-first architecture is used with a ring oscillator to reduce the total power consumption. A dual mixer is used to set the LO at half of the input RF frequency, leading to significant power savings in the LO and its buffers. The top level block diagram of the LC based BLE back-channel receiver is shown in Fig. 7. This architecture enables the fast frequency hopping by utilizing an RF LNA and an LC oscillator to reduce the noise and improve the frequency stability, respectively. The receiver selectivity is enhanced by limiting the baseband amplifiers bandwidth to 1 MHz.

The RO back-channel receiver was fabricated in a 65 nm LP CMOS process. The receiver has a sensitivity of -57.5 dBm for a BER of 10<sup>-3</sup>. Fig. 10 (a) demonstrates the signal-to-interference (SIR) performance, which is measured with a wanted signal 3 dB over the sensitivity level and with a GFSK modulated. The interference rejection was measured to be -4, -20, and -30 dB for the 1<sup>st</sup>, 5<sup>th</sup>, and 10<sup>th</sup> BLE adjacent channels, respectively. The total power consumption is 150 μW using 0.9 V and 1.1 V supplies for digital and analog blocks, respectively, with 120 μW

dissipated by the LO (including its buffers) that runs at 1.2 GHz, the digital FLL, and the LO frequency dividers. The analog baseband consumes the remaining  $30~\mu W$ .

The second prototype, which uses an LC oscillator, was fabricated in a 40nm CMOS process. It achieves a sensitivity of -82.2 dBm for a BER of 10<sup>-3</sup>. The SIR performance for a single advertisement channel is shown in Fig. 10 (a). The measured rejection ratios are -6, -28, and -46 dB for the 1st, 5th, and 10th BLE adjacent channels, which does not satisfy BLE's single channel block rejection performance (yellow line). On the other hand, Fig. 10 (b) shows the much improved (-32dB or lower) SIR performance when back-channel message communication is used with the message threshold set at two thirds of its maximum value. This measurement was done by sweeping the interferer frequency across the BLE frequency band while the desired signal is hopping its frequency between the three advertising channels. The worst case rejection ratio is -32 dB at 2414 MHz, which is the middle channel between CH37 and CH38. This result is expected since CH37 and CH38 are closer to each other than CH9. Including the worst case, the rejection ratio at all BLE channels is better than the blocker rejection requirements as set in the BLE specifications. The second prototype consumes 1.2 mW using 0.9 V and 1V supplies for digital and analog blocks, respectively. The dominating blocks are the LC oscillator and the LNA, which dissipate 500 μW and 380 μW, respectively. The remaining 320 μW is consumed by the analog and digital baseband. In both prototypes, the LO generation uses the highest percentage of power.

#### IV. WI-FI WAKE-UP RECEIVER

As mentioned previously, one of the challenges in ULP design is to still be able to communicate through an existing adopted standard, and communication through Wi-Fi can

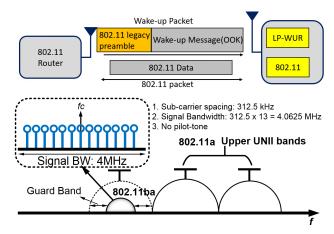

Fig. 11. Conceptual diagram of 802.11ba application (top), and Frequency floor planning of 802.11ba (bottom) [33].

be a good solution. Wi-Fi is one of the most ubiquitous wireless network protocol, however, its direct adoption into ULP IoT nodes is not a good solution due to its excessive active power consumption (>100mW). Even with heavy duty cycling of the 802.11 receiver, the average power is still too high for most ULP IoT applications, and the startup energy is often too great to make networking and latencies practical at ULP levels.

Recently, the 802.11ba task group established a new standard to reduce the average power of 802.11 receivers by integrating a low-power companion receiver with the main 802.11 receiver, which receives on-off keying (OOK) modulated signals (4 MHz, 13 subcarriers populated a long 20 MHz channel) from an 802.11 transmitter [35]. The power budget of an active Wi-Fi network can be significantly reduced by leveraging a wake-up receiver when the main Wi-Fi receiver remains asleep [35]. The

Fig. 12. System block diagram of the RO based 802.11ba low-power wake-up receiver.

frequency planning of the 802.11ba is shown in Fig. 11. Legacy Wi-Fi OFDM signals are generated by modulating sub-carriers in the frequency domain, converting sub-carrier symbols to the time domain, outputting them through a digital-to-analog converter (DAC), and finally up-converting the signal to RF. This OFDM architecture theoretically allows for a wide set of modulations such as OOK or M-ary FSK, although it is not specifically designed for this type of signal generation. By only updating the firmware of an 802.11 OFDM receiver [35], it is possible to map narrowband OOK or FSK symbols onto OFDM subcarriers, and disable the remaining unused sub-carriers.

For active wireless connectivity, the wake-up receiver has to achieve sensitivity of lowest data-rate of 802.11a transmitter, which is -82 dBm at data-rate of 6 Mb/s [12]. the minimum noise figure has been relaxed due to the relaxation of the SNR. This allows us to eliminate the power-hungry active RF gain stage in the wake-up receiver. Two mixer-first low power Wi-Fi wake-up receivers are recently reported that are based on RO [6], and LC oscillator [26].

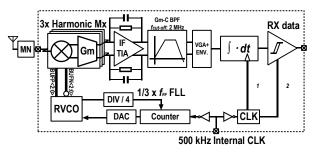

The RO based Wi-Fi wake-up receiver operates with 220µW while providing sensitivity of -83dBm, and -20dB SIR of 1st adjacent channel. The system block diagram of

Fig. 13. RF front-end of the receiver using 3<sup>rd</sup>-harmonics down-conversion

the RO based 802.11ba low-power wake-up receiver is shown in Fig. 12. The receiver is a passive mixer-first architecture with an off-chip matching network. Rather than using an LO-less RF energy detection architecture, which is common among ULP receivers because it results in the lowest active power, this receiver uses a ring-based voltage controlled oscillator (RVCO) to allow channel selection, improve selectivity, and operate at a lower active power than more power hungry LC-VCOs. The receiver receives 4 MHz wide OOK modulated RF signals in the 5.5-5.8 GHz band, compliant with the 802.11ba draft standard. These are down-converted with mixers that operate around 1/3 of the RF frequency, thus significantly reducing the active power of the RVCO and buffers. Odd harmonic down-conversion was chosen rather than even harmonic down-conversion because it has a better flicker noise corner vs. power trade-off of the RVCO [36].

To reduce power, no active RF gain stages are used. However, to maintain an adequate sensitivity, step-up transformer based matching network is implemented that provides voltage boost as well. After the three mixer stages, the down-converted IF signals are combined in the current domain before amplification and filtering in TIA. After the TIA, the IF signal is filtered with a -40 dB/dec roll off. Finally, the filtered IF signal is rectified, and integrated by baseband circuits, and the RX data is retrieved. The following sub-sections will explain the details of each system block.

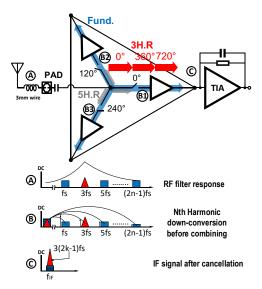

The spectrum diagram in Fig. 13 illustrates the behavior of each block that comprise the RF front-end. The RF signal is filtered, and impedance boosted as shown in Fig. 13(a). A commutating passive mixer has a non-linear response, so that at Fig. 13(b), when feeding an LO operating at  $f_{LO}$  to the mixer, it produces harmonic components at (2n -

1)  $\times f_{LO}$  (n is an integer). The actual passive mixer is differential pair that rejects even-order harmonics after down-conversion. Then, in Fig. 13(c), the down-converted signals after each mixer a summed in the current domain using IF low noise amplifiers (IF-LNA) transconductors. The construction and destruction of each harmonic components happen at Fig. 13(c). By combining signals from N-paths with mixers operating at a 360°/N phase difference each, the Nth harmonic signals at the outputs of the N mixers will be in-phase at baseband, while the other harmonic components are out-of-phase and cancel.

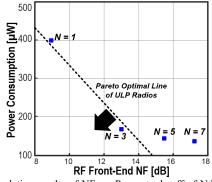

Simulation results of the power and NF for each harmonic passive mixer down-conversion is shown in Fig. 14. Increasing N beyond a value of 3 offers diminishing returns in NF vs. active power due to increased insertion loss of harmonic down-conversion gain. Comparing to edge combining duty-cycled frequency multi-plication mixer, this save decent amount of power because it uses small number of RF switches, and does not require any high-speed complex logic circuits. Considering noise analysis, and mismatch calibration, this architecture shows an optimal trade-off between performance and power with N=3, so that a  $3^{\rm rd}$  harmonic 3-path passive mixer is implemented.

Ideally, the front-end can perfectly reject the fundamental RF component while down-converting signals at the 3rd harmonic frequency. However, two mismatch factors affect this rejection ratio (3rd harmonic / fundamental). Mismatch in the delay cells of the RVCO generate phase mismatch which reduces the rejection ratio as this mismatch increases. However, the dominant factor is gain mismatch in the first inverter-based IF stage, which impacts the rejection ratio due to its common mode offset between IF-LNAs. According to simulation, a phase error less than 5% results in a rejection ratio up to 40 dB. Similar amount of rejection ratio is been observed for 5th, and 7th harmonics as well.

To minimize the gain mismatch, self-biased current steering differential IF amplifiers are used with fine resolution gain tuning. Without calibration, there were

Fig. 14. Simulation results of NF vs. Power trade-off of Nth harmonic Passive mixer RF Front-End. The line represents the Pareto optimal line of state-of-art ULP receivers.

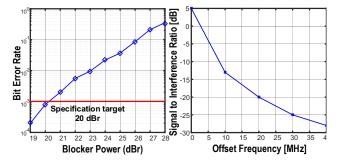

Fig. 15. BER versus blocker power of adjacent channel 1 (left), and signal-to-interference ratio (SIR) versus offset frequency (right).

large variations observed chip to chip, and the worst rejection ratio measured was 25 dB. After calibration, the worst rejection ratio measured was 37 dB, including passive RF matching before the RF front-end.

The receiver was fabricated in a CMOS 40 nm technology with an active area of 0.151 mm2. The BER is measured with alternated 802.11ba data. Measured sensitivity of the receiver is -83 dBm at BER of 10-3, and data-rate of 62.5 kbps. The sensitivity got 3 dB increment as the data-rate increased twice, which is 125 kbps. Interferer measurements are done with randomized binary data. The SIR of adjacent channel 1, and 2 are -20 dB, and -28 dB, respectively. The interference performance can be limited by the PN of the RVCO, thus, for narrow band receivers, SIR performance is dominated by PN rather than the order of the filter when the order is reasonably high (≥3).

#### V. CONCLUSION

In this paper, a summary of the recent design trends and techniques in low-power receivers design are presented. The power and performance trade-off is discussed and multiple approaches to design receivers that suit the requirements for IoT applications are demonstrated. Two receiver designs, which are compatible with the BLE and Wi-Fi standards, respectively, are presented. These receivers can support a decent communication range while meeting the interference rejection required by the standard with a power consumption in the 100 of  $\mu Ws$  range.

#### ACKNOWLEDGMENT

The material is supported by NSF under award number 1160483 and the US Department of Energy.

#### REFERENCES

- [1] E. Nilsson and C. Svensson, "Power Consumption of Integrated Low-Power Receivers," *IEEE J. Emerg. Sel. Top. Circuits Syst.*, vol. 4, no. 3, pp. 273–283, 2014.

- [2] A. M. Alghaihab, H. Kim, and D. D. Wentzloff, "Analysis of Circuit Noise and Non-Ideal Filtering Impact on Energy Detection Based Ultra-Low-Power Radios Performance," *IEEE Trans.* Circuits Syst. II Express Briefs, vol. 65, no. 12, pp. 1924–1928, Dec. 2018

- [3] A. Sai et al., "A 5.5 mW ADPLL-Based Receiver With a Hybrid

- Loop Interference Rejection for BLE Application in 65 nm CMOS," IEEE J. Solid-State Circuits, vol. 51, no. 12, pp. 3125-3136, Dec. 2016.

- [4] Z. Weng et al., "400-MHz/2.4-GHz Combo WPAN Transceiver IC for Simultaneous Dual-Band Communication With One Single Antenna," IEEE Trans. Circuits Syst. I Regul. Pap., vol. 65, no. 2, pp. 745-757, Feb. 2018.

- [5] A. Alghaihab, Y. Shi, J. Breiholz, H. Kim, B. H. Calhoun, and D. D. Wentzloff, "Enhanced Interference Rejection Bluetooth Low-Energy Back-Channel Receiver With LO Frequency Hopping, IEEE J. Solid-State Circuits, vol. 54, no. 7, pp. 2019–2027, Jul.

- [6] J. Im, H. Kim, and D. D. Wentzloff, "A 220-  $\mu$ W -83-dBm 5.8-GHz Third-Harmonic Passive Mixer-First LP-WUR for IEEE 802.11ba," IEEE Trans. Microw. Theory Tech., vol. 67, no. 7, pp.

- [7] J. Moody et al., "Interference Robust Detector-First Near-Zero Power Wake-Up Receiver," IEEE J. Solid-State Circuits, vol. 54, no. 8, pp. 2149-2162, 2019.

- J. Moody et al., "A -76dBm 7.4nW wakeup radio with automatic offset compensation," in 2018 IEEE International Solid - State Circuits Conference - (ISSCC), 2018, pp. 452-454.

- V. Mangal and P. R. Kinget, "28.1 A 0.42nW 434MHz -79.1dBm Wake-Up Receiver with a Time-Domain Integrator," in 2019 IEEE International Solid-State Circuits Conference - (ISSCC), 2019, pp. 438 - 440

- [10] V. Mangal and P. R. Kinget, "A -80.9dBm 450MHz Wake-Up Receiver with Code-Domain Matched Filtering using a Continuous-Time Analog Correlator," in 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2019, pp. 259-262.

- [11] N. E. Roberts et al., "26.8 A 236nW -56.5dBm-sensitivity bluetooth low-energy wakeup receiver with energy harvesting in 65nm CMOS," in 2016 IEEE International Solid-State Circuits Conference (ISSCC), 2016, pp. 450-451.

- [12] E. Alpman et al., "802.11g/n Compliant Fully Integrated Wake-Up Receiver With -72-dBm Sensitivity in 14-nm FinFET CMOS," IEEE J. Solid-State Circuits, vol. 53, no. 5, pp. 1411-1422, May

- [13] C. Salazar, A. Cathelin, A. Kaiser, and J. Rabaey, "A 2.4 GHz Interferer-Resilient Wake-Up Receiver Using A Dual-IF Multi-Stage N-Path Architecture," IEEE J. Solid-State Circuits, vol. 51, no. 9, pp. 2091-2105, 2016.

- [14] J. Im, H. Kim, and D. D. Wentzloff, "A 335µW -72dBm receiver for FSK back-channel embedded in 5.8GHz Wi-Fi OFDM packets," in 2017 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2017, pp. 176–179.

- [15] R. Liu et al., "An 802.11ba 495µW -92.6dBm-Sensitivity Blocker-Tolerant Wake-up Radio Receiver Fully Integrated with Wi-Fi Transceiver," in 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2019, pp. 255-258.

- [16] A. Kosari, M. Moosavifar, and D. D. Wentzloff, "A  $152\mu W$ -99dBm BPSK/16-QAM OFDM Receiver for LPWAN Applications," in 2018 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2018, pp. 303-306.

- [17] D. D. Wentzloff, "Low Power Radio Survey,." [Online]. www.eecs.umich.edu/wics/low\_power\_radio\_survey.html.

- [18] J. Moody et al., "A -106dBm 33nW Bit-Level Duty-Cycled Tuned RF Wake-up Receiver," in 2019 Symposium on VLSI Circuits, 2019, pp. C86-C87.

- [19] P. P. Wang and P. P. Mercier, "28.2 A 220µW -85dBm Sensitivity BLE-Compliant Wake-up Receiver Achieving -60dB SIR via Single-Die Multi- Channel FBAR-Based Filtering and a 4-Dimentional Wake-Up Signature," in 2019 IEEE International Solid- State Circuits Conference - (ISSCC), 2019, pp. 440-442.

- [20] J. Moody and S. M. Bowers, "Triode-mode Envelope Detectors for Near Zero Power Wake-up Receivers," in 2019 IEEE MTT-S

- International Microwave Symposium (IMS), 2019, pp. 1499-1502. [21] C. Bryant and H. Sjöland, "A 0.55 mW SAW-Less Receiver Front-

- End for Bluetooth Low Energy Applications," IEEE J. Emerg. Sel. Top. Circuits Syst., vol. 4, no. 3, pp. 262-272, 2014.

- [22] S. Lee, I. Choi, H. Kim, and B. Kim, "A Sub-mW Fully Integrated Wide-Band Receiver for Wireless Sensor Network," IEEE Microw. Wirel. Components Lett., vol. 25, no. 5, pp. 319-321, May 2015.

- [23] J. Im, H. Kim, and D. D. Wentzloff, "A 217µW -82dBm IEEE 802.11 Wi-Fi LP-WUR using a 3rd- Harmonic Passive Mixer," in 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2018, pp. 172–175.

- [24] M. Rahman and R. Harjani, "A Sub-1-V 194-µW 31-dB FOM 2.3-2.5-GHz Mixer-First Receiver Frontend for WBAN With Mutual Noise Cancellation," IEEE Trans. Microw. Theory Tech., vol. 64, no. 4, pp. 1102-1109, Apr. 2016.

- [25] T. Abe et al., "An ultra-low-power 2-step wake-up receiver for IEEE 802.15.4g wireless sensor networks," in 2014 Symposium on VLSI Circuits Digest of Technical Papers, 2014, pp. 1-2.

- [26] J. Im, H. Kim, and D. D. Wentzloff, "A 470µW -92.5dBm OOK/FSK Receiver for IEEE 802.11 WiFi LP-WUR," in ESSCIRC 2018 - IEEE 44th European Solid State Circuits Conference (ESSCIRC), 2018, pp. 302-305.

- [27] A. Alghaihab, J. Breiholz, H. Kim, B. Calhoun, and D. D. Wentzloff, "A 150 μW -57.5 dBm-Sensitivity Bluetooth Low-Energy Back-Channel Receiver with LO Frequency Hopping," in 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2018, pp. 324-327.

- [28] N. E. Roberts, M. C. Kines, and D. D. Wentzloff, "A 380µW Rx, 2.6mW Tx 433MHz FSK transceiver with a 102dB link budget and bit-level duty cycling," in 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2015, pp. 171-174.

- [29] H. Yi, W. Yu, P. Mak, J. Yin, and R. P. Martins, "A 0.18-V 382- $\mu W$  Bluetooth Low-Energy Receiver Front-End With 1.33-nW Sleep Power for Energy-Harvesting Applications in 28-nm CMOS," IEEE J. Solid-State Circuits, vol. 53, no. 6, pp. 1618-1627, 2018.

- [30] A. Selvakumar, M. Zargham, and A. Liscidini, "13.6 A 600µW Bluetooth low-energy front-end receiver in 0.13µm CMOS technology," in 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers, 2015, pp. 1-3.

- [31] A. H. M. Shirazi, H. M. Lavasani, M. Sharifzadeh, Y. Rajavi, S. Mirabbasi, and M. Taghivand, "A 980µW 5.2dB-NF current-reused direct-conversion bluetooth-low-energy receiver in 40nm CMOS," in 2017 IEEE Custom Integrated Circuits Conference (CICC), 2017, pp. 1-4.

- [32] H. S. Kim and D. D. Wentzloff, "Back-Channel Wireless Communication Embedded in WiFi-Compliant OFDM Packets," IEEE J. Sel. Areas Commun., vol. 34, no. 12, pp. 3181–3194, 2016.

- [33] J. Prummel et al., "13.3 A 10mW Bluetooth Low-Energy transceiver with on-chip matching," in 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers, 2015, pp. 1-3.

- [34] H. Liu et al., "An ADPLL-centric bluetooth low-energy transceiver with 2.3mW interference-tolerant hybrid-loop receiver and 2.9mW single-point polar transmitter in 65nm CMOS," in 2018 IEEE International Solid - State Circuits Conference - (ISSCC), 2018, pp. 444-446.

- [35] M. Park, "Wake-Up Radio (WUR) Operation," 2016. [Online]. Available: www.ieee802.org/11/Reports/tgba update.htm.

- [36] J. Yin, P. Mak, F. Maloberti, and R. P. Martins, "2.7 A 0.003mm2 1.7-to-3.5GHz dual-mode time-interleaved ring-VCO achieving 90to-150kHz 1/f3 phase-noise corner," in 2016 IEEE International Solid-State Circuits Conference (ISSCC), 2016, pp. 48-49.