# A 486 µW All-Digital Bluetooth Low Energy Transmitter with Ring Oscillator Based ADPLL for IoT applications

Xing Chen<sup>1</sup>, Jacob Breiholz<sup>2</sup>, Farah Yahya<sup>2</sup>, Christopher Lukas<sup>2</sup>, Hun-Seok Kim<sup>1</sup>, Benton Calhoun<sup>2</sup>,

David Wentzloff<sup>1</sup>

<sup>1</sup>University of Michigan, Ann Arbor, USA <sup>2</sup>University of Virginia, Charlottesville, USA

Abstract—this paper presents an all-digital Ring Oscillator (RO) based Bluetooth Low-Energy (BLE) transmitter (TX) for ultra-low-power radios in short range IoT applications. It employs a wideband ADPLL featuring an  $f_{RF}/4$  RO, with an embedded 5-bit TDC. A 4X frequency edge combiner is used to generate the 2.4GHz signal. This helps reduce the power consumption and enhance its phase noise performance at the same time. A switch-capacitor PA is optimized for high efficiency in low power mode. The TX is designed at the phase noise limit for BLE and in low power mode it consumes 486  $\mu$ W while configured as a non-connectable advertiser, which has been validated by wirelessly communicating beacon messages to a mobile phone.

Index Terms— Bluetooth Low-Energy (BLE), Ultra-low-power radios, IoT, Transmitter, Ring Oscillator, ADPLL, Phase Noise, Switch-capacitor PA.

#### I. INTRODUCTION

With the increasing demand for inter-connected IoT devices, ultra-low-power (ULP) radios, especially those with standard compatibilities, are dramatically needed in wireless sensors for a wide range of applications. Bluetooth Low-Energy (BLE) is widely used as the wireless interface for ULP IoT devices, yet due to phase noise (PN) limitations and the complexity of the LO design in a BLE transceiver, state-of-the-art BLE radios consume several milliwatts [1-4], limiting battery lifetime in such applications. Thus, in many short range and energyharvesting applications, such as wearable sensor nodes and implantable medical devices, current BLE radios are still too high power to be adopted in a large scale. Asymmetric communications are normally used in such systems, but they always suffer from interference and bulky base stations [5]. Thus, by making an asymmetric BLE network in its advertising channel will not only reduce the power consumption of BLE transmitters (TX) in the sensor node to its limit, but could also help resolve the interference and base station issues in ULP wireless sensor systems.

All reported BLE TX use LC oscillators (LCVCO) due to their inherent advantage in phase noise over ring oscillators (RO). However, their power consumption is strictly limited by the quality factor of the integrated LC tank. Furthermore, the PN of LCVCOs at the minimum power point is still 30-40dB better than what is required for BLE based on BER alone. Open loop LCVCOs has been adopted in recent BLE designs to reduce power, but these

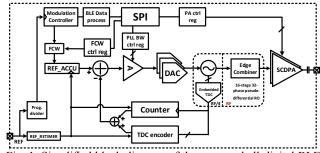

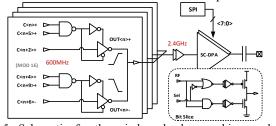

are still limited by the intrinsic high power of LCVCOs. ROs, on the other hand, have not been demonstrated in BLE designs because of their typically worse PN performance. However, they have the advantage of being able to trade off power for PN and they can further benefit from scaling. This paper explores the PN and PLL trade-offs as they relate to the BLE specs, which results in a PN limit achievable by a RO-based PLL. An all-digital RO-based BLE transmitter, as shown in Fig. 1, is presented that meets this PN limit with a ULP wideband ADPLL and an efficiency-optimized SCDPA. A 32-phase  $f_{RF}/4$  RO, that not only forms a 5-bit embedded TDC but also serves as a 4X frequency edge combiner, is adopted to reduce the PLL power and improve its PN performance. The BLE TX consumes 486 µW while configured as a non-connectable advertiser, which is desirable for short-range TX-only beacon devices in an asymmetric BLE network. Its functionality has been validated communicating beacon messages to a mobile phone.

This paper is organized as follows: section II talks about the analysis of PN limit for BLE. Section III discusses the details of design considerations in system level and circuit level to achieve low power and the required noise performance. Section IV discusses the measurement results and the comparison to the state-of-the-art. Finally, section V draws the conclusion.

Fig. 1. Simplified block diagram of the proposed all-digital BLE TX

#### II. PHASE NOISE ANALYSIS FOR BLE

Based on the relationship between PN, period jitter and instantaneous frequency variation [6-7], the standard deviation of the frequency variation,  $\sigma_f$ , can be calculated by integrating the PN falling into the RX filter BW:

$$\sigma_f = f_0^2 \sigma_\tau = \sqrt{\int_0^{BW} 2L(f) f^2 sinc^2 \left(\frac{\pi f}{f_0}\right) df}$$

(1)

where L(f) is PN at certain offset,  $\sigma_f$ ,  $\sigma_\tau$  represent the standard deviation of frequency variation and jitter, and  $f_0$ is the center frequency. Applying this to practical radio systems, if the LO is an open loop oscillator, and ignore flicker noise effect, the resulting frequency variation can be simplified as:

$$\sigma_f = \sqrt{2BW_{rx}L(f)f^2} \tag{2}$$

As for PLL regulated cases, with different PLL BW, the relations can be simplified as (3) and (4) assuming a constant in-band phase noise response:

$$\sigma_{f} = f_{0}^{2} \left\{ \frac{\frac{1}{2\pi^{3} f_{0}} \left( \frac{2\pi BW_{pll}}{f_{0}} - \sin\left( \frac{2\pi BW_{pll}}{f_{0}} \right) \right) + \frac{2}{f_{0}^{4}} \left( BW_{rx} - BW_{pll} \right) BW_{pll}^{2} \right\} L_{in}$$

(3)

$$\sigma_{f} = f_{0}^{2} \sqrt{\frac{1}{2\pi^{3} f_{0}} \left( \frac{2\pi BW_{rx}}{f_{0}} - \sin\left( \frac{2\pi BW_{rx}}{f_{0}} \right) \right) L_{in}}$$

(4)

$$\sigma_f = f_0^2 \sqrt{\frac{1}{2\pi^3 f_0} \left(\frac{2\pi B W_{rx}}{f_0} - \sin\left(\frac{2\pi B W_{rx}}{f_0}\right)\right) L_{in}}$$

(4)

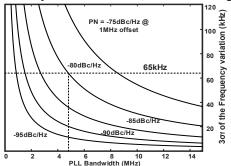

where  $L_{in}$  is the in-band PN level. [8] has also found this in an integrating format. Considering this in a high SNR regime since the target communication range is within 1-2 meters, PN is the dominant noise source. So from the analysis above, the BLE spec could be achieved by an ULP RO regulated by a wide band PLL, as shown in Fig. 2.

Fig. 2. Simulated PLL bandwidth requirement for different phase noise levels

### III. SYSTEM LEVEL DESIGN AND CIRCUIT DETAILS

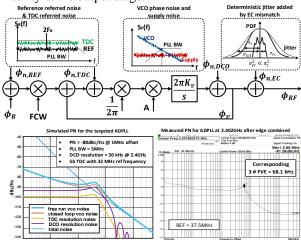

Fig. 3 shows the top-level block diagram of the proposed design and its major noise sources. To achieve the targeted frequency variation error with the RO, a 5MHz bandwidth ADPLL for aggressive in-band phase noise suppression is implemented. It features a fast settling time and direct reference phase modulation since the PLL BW is much larger than the modulation BW. Several techniques are used to save the PLL power and enhance its in-band PN at the same time. The RO is designed at a frequency of  $f_{RF}/4$  and implemented with a 16-stage pseudo-differential architecture with 32 phases directly used as an embedded TDC. Its phases are also used in a windowed edge combiner for 4X frequency multiplication to produce the 2.4GHz RF frequency. The lower frequency RO saves the power of the frequency divider. And it also prevents the noise folding effect from happening when the noisy phases are subsampled and folded by the divider in the traditional divider based PLL, thus improving in-band PN performance. At the same time, the high power TDC and its delay normalization circuits are also saved, and the TDC performance can be relaxed by dealing with the same amount of jitter at a lower frequency while maintaining the same resolution. The edge combiner consumes much less power compared to a TDC, and it can maintain the low flicker noise corner from the low frequency RO, which will again, enhance the in-band phase noise [9].

Even though extra deterministic jitter will be introduced because of the mismatches in the different paths of the edge combiner, as shown in Fig. 3, this mismatch is much smaller than the random jitter from the high PN RO. Since this jitter is not correlated with the random jitter, the windowed edge combiner won't affect the overall RF performance. And due to periodical phase shifts, the edge combiner will also introduce spurs at  $\pm f_{RF}/4$  off the center frequency with the spur level equal to  $20\log(\delta T_0/T_0)$  [10]. In this design, the edge combiner introduced jitter is within 1 ps, thus mismatch introduced spurs are smaller than -50dBc, which are almost negligible compared to PA nonlinearity at the output stage.

Fig. 3. System-level (top) noise analysis and PLL design & measurement (bottom)

Fig. 4. Circuit-level noise analysis for critical noise sources Critical noise sources are modelled for the PLL, as shown in Fig. 3. The PLL is designed to achieve a 5MHz

BW with a -85dBc/Hz in-band PN. And the BW is programmable by changing the loop filter gain through an SPI interface, as shown in Fig. 1. Measured results show great agreement with the design. The phase noise performance corresponds to a 68.1 kHz  $3\sigma_f$  frequency error, and demonstrates successful BLE communication under the BLE spectrum mask. With this  $f_{RF}/4$  RO and edge combiner architecture with its 4X phases embedded TDC, the PLL controller's power consumption is as low as 253  $\mu$ W in a 40nm technology. Moreover, with the scale of technology, this number could be further improved.

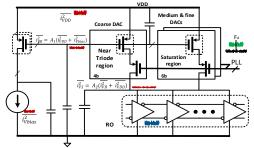

Fig. 4 shows the major noise sources at the transistor level that need to be carefully dealt with. Since the PLL BW is very high for in-band PN suppression and direct reference phase modulation, the decap on the virtual VDD of the RO has to be fairly small to keep the PLL loop stable, thus plenty of noise from the supply and the bias network will pass through. To deal with this, the coarse DAC bank is designed at the edge of the triode region to minimize the noise gain while the medium and fine DAC banks are designed in the saturation region to keep the required tuning linearity while the PLL is locked. Additional large decaps are added to the gate of the DAC cells to filter the accumulated supply and bias noise. The medium and fine current steering DACs are 6b each that covers 70 MHz range with approximately 20 kHz LSB tuning step for the RO and the coarse DAC is 4b and can cover up to 300 MHz.

Fig. 5. Schematic for the windowed edge combiner and the switch-capacitor digital PA

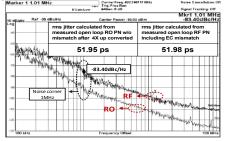

Fig. 6. Measured phase noise of the open loop RO and EC output due to mismatch

Fig. 5 shows the windowed EC and the SCDPA. 24 of the 32 RO phases are used to implement a windowed edge combiner. 6 phases are used for each rising and falling edge to be combined, in which the 2 windows are spaced by 4 RO delays and the window width is 5 delays to ensure all selected phases pass through in different PVT corners. Tristate gates are used to pass the selected phase and buffer

the interference from other phases. The measured phase noise for the open loop RO working at 493MHz before and after edge combining is shown in Fig. 6 and it shows that the combined RF output follows the same noise corner as the low frequency RO. The impact of the EC on the integrated PN jitter calculated from the phase noise measurement shown in Fig. 6 is 1.7ps and the resulting spurs are at -49.4dBc from calculation (cannot be directly measured with the PA). Both are insignificant compared to the PLL jitter and PA non-linearity. The low power SC-DPA is thermometer coded with 8-bit slices and is matched and optimized for the highest efficiency for -10dBm operation.

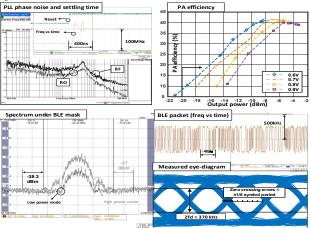

Fig. 7. Measurement results including PLL phase noise and settling time (top left), PA efficiency (top right), output spectrum @ 2.402GHz (bottom left), and captured BLE packets with eye diagram (bottom right)

#### IV. MEASUREMENT RESULT

Fig. 7 presents the measured PLL and the BLE TX performance. The PLL is locked at 600.5MHz and combined to 2.402GHz, with a BW larger than 5 MHz. With the large BW, the PLL settles within 0.4µs from reset, as shown in the frequency vs time measurement. The measured PA drain efficiencies are also shown. It consumes 107 μW when the output is -19.2 dBm with a 10.8% efficiency using a 0.6V supply. In high power mode, it can deliver -3.3 dBm while consuming 1.2 mW with a 39% efficiency using a 0.9V supply. The maximum efficiency of 41% is achieved at around -10dBm output power. The TX spectrum is also measured while transmitting a repeated BLE packet, which meet the BLE spectrum mask requirement. The measured frequency vs. time for part of the BLE packets are also shown. The eye-diagram is calculated from the captured frequency domain signal. The phase noise from the RO does degrade the eye performance, but as designed, both the symbol timing and frequency error meet the BLE communication limit.

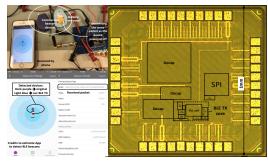

Fig. 8 shows the wireless test setup. Here, the BLE TX is configured to transmit an iBeacon message, which is

picked up by the iBeacon app, and shows the correct packet information. While working at the low power mode with a 37.5MHz off chip reference, the RO with the DAC bias network consumes 126  $\mu$ W, and the PLL blocks with the edge combiner consumes 253  $\mu$ W. The all-digital RO based BLE TX consumes a total 486  $\mu$ W power with an active area of only 0.0166 mm² in a 40nm technology, as shown in the die photo. The comparison to the state-of-the-art is shown in Table I.

Fig. 8. Wireless test setup and die photo

## V. CONCLUSION

In this work, an all-digital ULP BLE TX with a  $f_{RF}/4$  RO based TDC-less ADPLL and 4X edge combiner is presented. Ring Oscillator is proved in theory and demonstrated in circuits to be feasible for BLE TX design with low power. The transmitter consumes 486  $\mu$ W in its low power mode while talking to a phone and is extremely low cost due to the implementation with RO. Moreover, because of the all-digital nature of this design, it can further benefit from technology scaling, and is suitable for short-range wireless sensor networks in ULP IoT applications.

#### ACKNOWLEDGMENT

This work is supported by NSF (EEC-1160483).

#### REFERENCES

- Y. H. Liu et al., "A 3.7mW-RX 4.4mW-TX fully integrated Bluetooth Low-Energy/IEEE802.15.4/proprietary SoC with an ADPLL-based fast frequency offset compensation in 40nm CMOS," ISSCC, pp. 236-237, Feb. 2015

J. Prummel et al., "A 10mW Bluetooth Low-Energy

- [2] J. Prummel et al., "A 10mW Bluetooth Low-Energy transceiver with on-chip matching," ISSCC, pp. 238-239, Feb. 2015

- [3] T. Sano et al., "A 6.3mW BLE transceiver embedded RX image-rejection filter and TX harmonic-suppression filter reusing on-chip matching network," ISSCC, pp. 240-241, Feb. 2015

- [4] M. Babaie et al., "A Fully Integrated Bluetooth Low-Energy Transmitter in 28 nm CMOS With 36% System Efficiency at 3 dBm," in IEEE Journal of Solid-State Circuits, vol. 51, no. 7, pp. 1547-1565, July 2016.

- [5] A. Roy et al., "A 6.45 μW Self-Powered SoC With Integrated Energy-Harvesting Power Management and ULP Asymmetric Radios for Portable Biomedical Systems," in IEEE Transactions on Biomedical Circuits and Systems, vol. 9, no. 6, pp. 862-874, Dec. 2015.

- [6] A. A. Abidi, "Phase Noise and Jitter in CMOS Ring Oscillators," in IEEE Journal of Solid-State Circuits, vol. 41, no. 8, pp. 1803-1816, Aug. 2006.

- [7] X. Chen, et al., "An analysis of phase noise requirements for ultra-low-power FSK radios," RFIC, pp. 37-40. June 2017.

- [8] Y. H. Liu et al., "An Ultra-Low Power 1.7-2.7 GHz Fractional-N Sub-Sampling Digital Frequency Synthesizer and Modulator for IoT Applications in 40 nm CMOS," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 5, pp. 1094-1105, May 2017.

- [9] J. Yin, et al., "A 0.003mm2 1.7-to-3.5GHz dual-mode timeinterleaved ring-VCO achieving 90-to-150kHz 1/f3 phasenoise corner," ISSCC, pp. 48-49. Feb. 2016.

- [10] B. M. Helal, et al., "A Low Jitter Programmable Clock Multiplier Based on a Pulse Injection-Locked Oscillator With a Highly-Digital Tuning Loop," in IEEE Journal of Solid-State Circuits, vol. 44, no. 5, pp. 1391-1400, May 2009

TABLE I

COMPARISON WITH STATE-OF-THE-ART BLE TRANSMITTERS

|                            | Th                        | is work        | ISSCC15[1] | ISSCC15[2] | ISSCC15[3] | JSSC16[4] |        |

|----------------------------|---------------------------|----------------|------------|------------|------------|-----------|--------|

| Technology (nm)            | 40                        |                | 40         | 55         | 40         | 28        |        |

| Supply voltage (v)         | 0.6-0.9                   |                | 1          | 0.9-3.3    | 1.1        | 0.5/1     |        |

| PLL REF frequency<br>(MHz) | 32-48<br>(37.5 as tested) |                | 32         | 16         | 32         | 5/40      |        |

| PLL settling time (μs)     | 0.4                       |                | 15         | 15         | N/A        | 14        |        |

| PLL In-band PN<br>(dBc/Hz) | -85                       |                | -90        | N/A        | N/A        | -92/-101  |        |

| Max output power (dBm)     | -10.6<br>-3.3             | @0.6V<br>@0.9V | -2/1       | 0          | 0          | 3         |        |

| Max PA efficiency          | 41%                       |                | 25%        | 30%        | <30%       | 41%       |        |

| TX Power consumption       | 0.49mW                    | 1.55mW         | 4.2mW      | 10.1mW     | 7.7mW      | 4.4mW     | 3.8mW* |

|                            | @-19dBm                   | @-3dBm         | @-2dBm     | @0dBm      | @0dBm      | @0dBm     | @-3dBm |

| Core Area (mm²)            | 0.0166                    |                | 0.6**      | 0.6**      | 0.6**      | 0.65      |        |

<sup>\*</sup>Estimated from PA efficiency

<sup>\*\*</sup>Estimated from die photo for only TX